Paul Jespers

ACSP

Analog Circuits And Signal Processing

# The g<sub>m</sub>/l<sub>D</sub> Methodology, a sizing tool for low-voltage analog CMOS Circuits

The semi-empirical and compact model approaches

The  $g_m/I_D$  Methodology, A Sizing Tool for Low-voltage Analog CMOS Circuits

#### ANALOG CIRCUITS AND SIGNAL PROCESSING SERIES

Consulting Editor: Mohammed Ismail. Ohio State University

For other titles published in this series, go to www.springer.com/series/7381

## The $g_m/I_D$ Methodology, A Sizing Tool for Low-voltage Analog CMOS Circuits

The Semi-empirical and Compact Model Approaches

By

Paul G.A. Jespers Université Catholique de Louvain Louvain-la-Neuve, Belgium

Prof. Paul G.A. Jespers Université Catholique de Louvain Louvain-la-Neuve Belgium Paul.Jespers@uclouvain.be

Additional material to this book can be downloaded from http://extra.springer.com.

ISBN 978-0-387-47100-6 e-ISBN 978-0-387-47101-3 DOI 10.1007/978-0-387-47101-3 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2009940107

#### © Springer Science+Business Media, LLC 2010

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

to Denise and to my parents Oscar Jespers and Mia Carpentier

#### **Foreword**

IC designers appraise currently transistors sizes while having to fulfill simultaneously a large number of objectives like a prescribed gain-bandwidth product, minimal power consumption, minimal area, low-voltage design, dynamic range, non-linear distortion, etc. Making appropriate decisions is not always obvious. How to meet gain-bandwidth specifications while minimizing power consumption of an Op. Amp without area penalty? Should moderate inversion be preferred to strong inversion? Is sizing an art or a mixture of design experience and repeated simulations? Or is it a constrained multivariate optimization problem? Optimization algorithms are attractive without doubt but they require translating not always well-defined concepts into mathematical expressions. The interactions amid semiconductor physics and systems are not always easy to implement.

The objective of the book is to devise a methodology enabling to fix currents and transistors widths of CMOS analog circuits so as to meet specifications such as gain-bandwidth while optimizing attributes like low power and small area. A special attention is given to low-voltage circuits. The sizing method takes advantage of the  $g_m/I_D$  ratio and makes use of either 'semi-empirical' data or compact models. The 'semi-empirical' approach utilizes large look-up tables derived from physical measurements carried out on real transistors or advanced models. The compact model approach offers the possibility to make use of analytic expressions. Unfortunately when it comes to real transistors, especially sub-micron devices, this isn't true anymore. Other means are necessary to keep track of high order effects without the risk to loose the inherent simplicity of compact models. Bias dependent instead of constant parameters offer the possibility to extend the validity of a model like the E.K.V. model.

In the first chapter, the Intrinsic Gain Stage, is sized making use of the classical strong and weak inversion large signal models of MOS transistors. This leaves open the moderate inversion region, a region that offers the best compromises generally as far as power consumption and sizes. To be able to size circuits in moderate inversion, we need a reliable large signal MOS model. The Charge Sheet Model that is considered in Chapter 2 is an invaluable tool for understanding the mechanisms governing current in MOS transistors, but it is not fitted for real transistors for it relies on the gradual channel approximation and makes use of mathematical expressions that are too complicated. The MATLAB tools that are available under

viii Foreword

'extras.springer.com' overcome the mathematical aspects and offer the possibility to perform 'ideal experiments'. Some of the abstract aspects of the Charge Sheet Model moreover are bridged in Chapter 3 by the introduction of a graphical representation of the drain current that combines physical aspects and practical circuits.

The E.K.V. basic model discussed in Chapter 4, offers clearly more flexibility. It is an approximation of the Charge Sheet Model and a forerunner of what is viewed nowadays as compact Surface Potential Models. The model paves the way towards analytical expressions not only for the drain current but also for the terminal voltages whatsoever the mode of operation of the transistor, whether saturated or not. Unfortunately, the simple E.K.V. model is a gradual channel model like the Charge Sheet Model, unfit thus for real transistors, in particular short channel device.

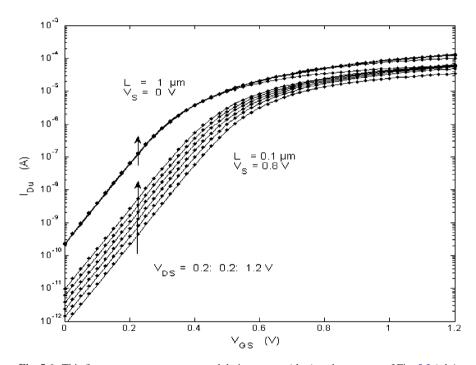

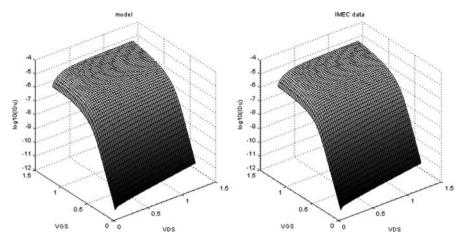

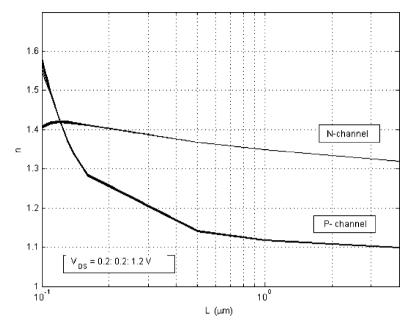

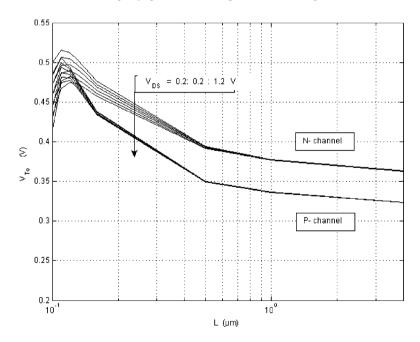

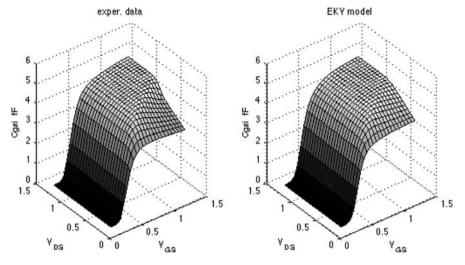

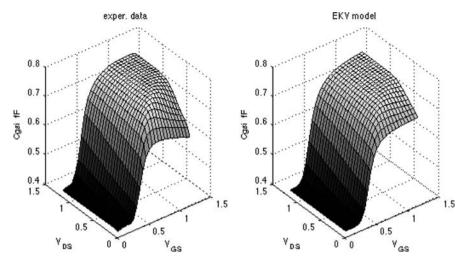

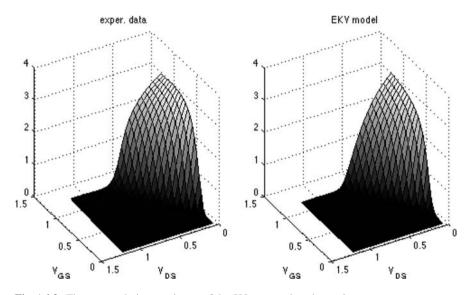

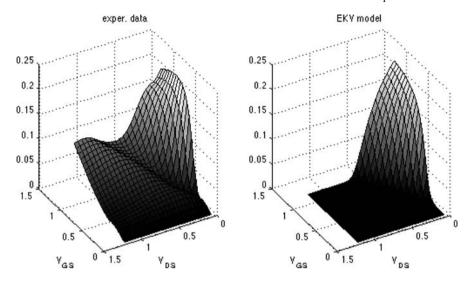

The fact that drain currents predicted by the E.K.V. compact model look so similar to real drain currents opens the question whether the model could not be extended to real devices. In Chapter 5, we show that currents very close to real drain currents can be predicted when the parameters of the E.K.V. model vary with bias, even with 100 nm devices. The explanation may be the quasi-one-dimensional nature of the channel opposed to the two-dimensional space charge below the inversion layer. As a result, gradual channel conditions prevail in the inversion layer any longer than in the space charge when the gate length is shrinking. An algorithm is proposed to acquire the model parameters.

The Intrinsic Gain Stage is reconsidered in Chapter 6 in the light of the variable parameters compact model. Currents and transistor width obtained by means of the compact model reproduce very closely the values obtained by means of the 'semi-empirical' method. A series of examples considering a low-frequency and a one GHz gain-bandwidth product I.G.S. are described.

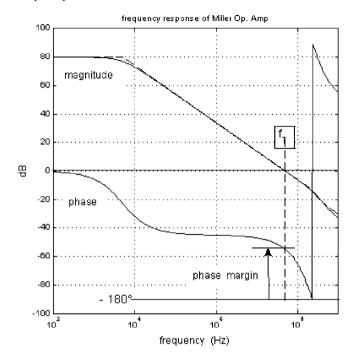

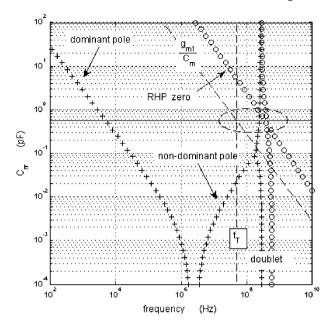

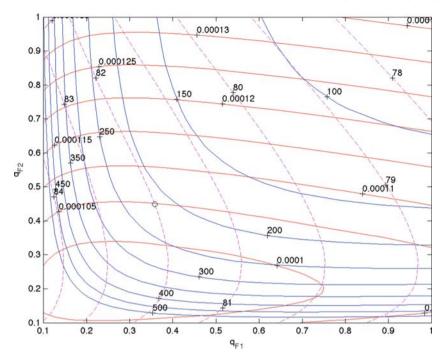

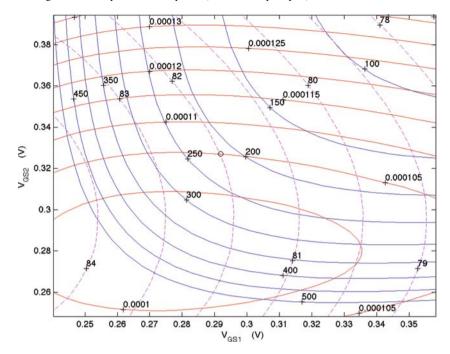

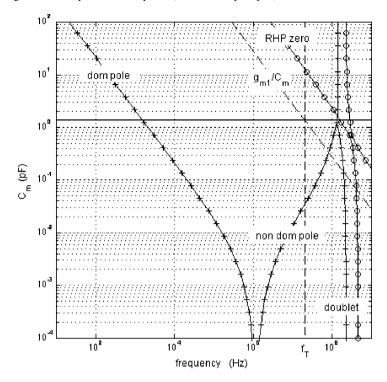

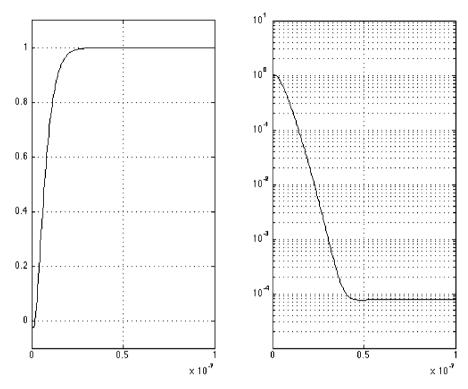

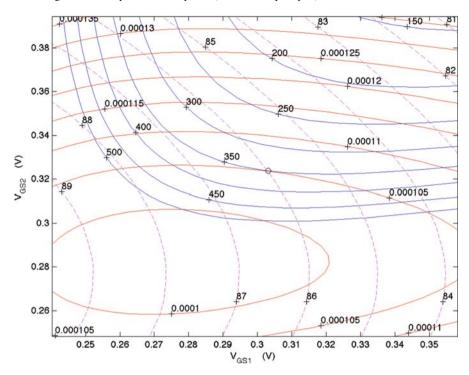

The remaining Chapters 7 and 8 extend the method respectively to the commongate stage and to the basic Miller Op. Amp. The latter illustrates how to meet both, specifications and attributes. Specifications concern the gain-bandwidth product and phase margin, attributes low power and area. These determine optimal regions in the 2D sizing space defined by the first and second stages of the Miller Op. Amp. A MATLAB file compares design strategies.

I want to express my gratitude to Piet Wambacq for the opportunity he gave me to check the validity of the variable parameter E.K.V. model on a 90 nm technology developed by IMEC. I am also very thankful Prof. Gilbert Declerck, former President CEO and Ludo Deferm, executive vice-president of IMEC, who gave me permission to publish the results and the data listed under the 'extras.springer.com'.

My sincere thanks go to Prof. Fernando Silveira who published in 1996 the first paper illustrating the potential of the  $g_m/I_D$  methodology. I want to thank him as well as Prof. A. Vladimirescu for the very detailed comments and suggestions they made of the first chapters. I also want to associate Prof. D. Flandre to my thanks owing to our long-term collaboration at the Microelectronics lab of the Université Catholique de Louvain.

Though the specific current put to use in the book is the one defined in the E.K.V. model, I owe much to two research groups. I am indebted to Prof. Eric Vittoz for the

Foreword ix

E.K.V. model, and to Prof. Carlos Galup-Montoro and Marcio C. Schneider for the A.C.M. model. I thank the supporters of the two models for motivating discussions and in particular the opportunity Prof. Montoro and Schneider gave me to visit them at the Federal University of Santa Catarina, Brasil.

Tervuren, July 2009

P. Jespers

### **Contents**

| 1 | Sizing the Intrinsic Gain Stage |                                                                   |    |  |

|---|---------------------------------|-------------------------------------------------------------------|----|--|

|   | 1.1                             | The Intrinsic Gain Stage                                          | 1  |  |

|   | 1.2                             | The Intrinsic Gain Stage Frequency Response                       | 1  |  |

|   | 1.3                             | 3 Sizing the Intrinsic Gain Stage                                 |    |  |

|   |                                 | 1.3.1 Sizing the I.G.S. with the Quadratic Model                  | 4  |  |

|   |                                 | 1.3.2 Sizing the I.G.S. by Means of the Weak                      |    |  |

|   |                                 | Inversion Model                                                   | 4  |  |

|   |                                 | 1.3.3 Sizing the I.G.S. in the Moderate Inversion Region          | 5  |  |

|   | 1.4                             | The $g_m/I_D$ Sizing Methodology                                  | 7  |  |

|   | 1.5                             | Conclusions                                                       | 8  |  |

| 2 | The                             | Charge Sheet Model Revisited                                      | 11 |  |

|   | 2.1                             | Why the Charge Sheet Model?                                       |    |  |

|   | 2.2                             | The Generic Drain Current Equation                                |    |  |

|   | 2.3                             | The Charge Sheet Model Drain Current Equation                     |    |  |

|   | 2.4                             | Common Source Characteristics                                     |    |  |

|   |                                 | 2.4.1 The $I_D(V_D)$ Characteristics                              | 15 |  |

|   |                                 | 2.4.2 The $I_D(V_G)$ Characteristic of the Saturated Transistor   |    |  |

|   |                                 | 2.4.3 Drift and Diffusion Contributions to the Drain Current      |    |  |

|   | 2.5                             | Weak Inversion Approximation of the Charge Sheet Model            | 18 |  |

|   | 2.6                             | The $g_m/I_D$ Ratio in the Common Source Configuration            |    |  |

|   | 2.7                             | Common Gate Characteristics of the Saturated Transistor           | 23 |  |

|   | 2.8                             | A Few Concluding Remarks Concerning the C.S.M                     | 24 |  |

| 3 | Grar                            | ohical Interpretation of the Charge Sheet Model                   | 25 |  |

|   | 3.1                             | A Graphical Representation of $I_D$                               |    |  |

|   | 3.2                             | More on the $V_T$ Curve.                                          |    |  |

|   | 3.3                             | Two Approximate Representations of $V_T$                          |    |  |

|   |                                 | 3.3.1 The 'Linear' Surface Potential Approximation                |    |  |

|   |                                 | 3.3.2 The 'Linear' Threshold Voltage $V_T$ Approximation          |    |  |

|   | 3.4                             | A Few Examples Illustrating the Use of the Graphical Construction |    |  |

|   |                                 |                                                                   |    |  |

xii Contents

|   |                  | 3.4.2                                                          | The MOS Source Follower                         | 32 |  |  |

|---|------------------|----------------------------------------------------------------|-------------------------------------------------|----|--|--|

|   |                  | 3.4.3                                                          | The CMOS Inverter                               | 33 |  |  |

|   |                  | 3.4.4                                                          | Small Signal Transconductances                  | 34 |  |  |

|   |                  | 3.4.5                                                          | CMOS Transmission Gates                         | 35 |  |  |

|   |                  | 3.4.6                                                          | How to Implement Quasi-linear Resistors         |    |  |  |

|   |                  |                                                                | with MOS Transistors                            | 36 |  |  |

|   |                  | 3.4.7                                                          | Source-Bootstrapping                            | 37 |  |  |

|   | 3.5              | A Close                                                        | er Look to the Pinch-Off Region                 |    |  |  |

|   | 3.6              |                                                                | sion                                            |    |  |  |

| 4 | Compact Modeling |                                                                |                                                 |    |  |  |

|   | 4.1              |                                                                | sic Compact Model                               |    |  |  |

|   | 4.2              | The E.I                                                        | K.V. Model                                      | 42 |  |  |

|   |                  | 4.2.1                                                          | The $V_T(V)$ Characteristic                     | 42 |  |  |

|   |                  | 4.2.2                                                          | The Drain Current                               | 45 |  |  |

|   |                  | 4.2.3                                                          |                                                 |    |  |  |

|   |                  | 4.2.4                                                          | Graphical Interpretation of the E.K.V. Model    |    |  |  |

|   | 4.3              | The Co                                                         | ommon Source Characteristics $I_D(V_G)$         |    |  |  |

|   | 4.4              |                                                                | and Weak Inversion Asymptotic                   |    |  |  |

|   |                  | _                                                              | simations Derived from the Compact              |    |  |  |

|   |                  |                                                                | *                                               | 50 |  |  |

|   | 4.5              | Checki                                                         | ng the Compact Model Against the C.S.M          | 50 |  |  |

|   |                  | 4.5.1                                                          | The Acquisition Algorithm (MATLAB Identif3.m)   |    |  |  |

|   |                  | 4.5.2                                                          | Verification                                    | 52 |  |  |

|   | 4.6              | Evaluat                                                        | tion of $g_m/I_D$                               | 54 |  |  |

|   | 4.7              | Sizing the Intrinsic Gain Stage by Means of the E.K.V. Model 5 |                                                 |    |  |  |

|   | 4.8              | The Common-Gate $g_{ms}/I_D$ Ratio                             |                                                 |    |  |  |

|   | 4.9              | An Earlier Compact Model                                       |                                                 |    |  |  |

|   | 4.10             | •                                                              |                                                 |    |  |  |

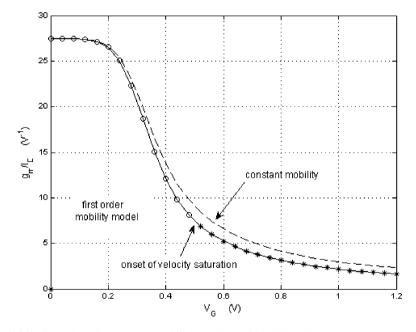

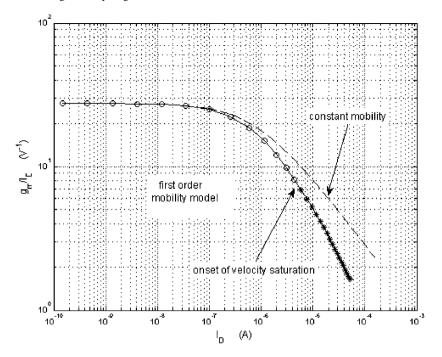

|   |                  | 4.10.1                                                         | The Impact of Mobility Degradation              |    |  |  |

|   |                  |                                                                | on the Drain Current                            | 59 |  |  |

|   |                  | 4.10.2                                                         | The Impact of Mobility Degradation              |    |  |  |

|   |                  |                                                                | on the $g_m/I_D$ Ratio                          | 64 |  |  |

|   |                  | 4.10.3                                                         | Sizing the Intrinsic Gain Stage in the Presence |    |  |  |

|   |                  |                                                                | of Mobility Degradation                         | 65 |  |  |

|   | 4.11             | Conclu                                                         | sion                                            |    |  |  |

| 5 | The I            | Real Trai                                                      | nsistor                                         | 67 |  |  |

|   | 5.1              |                                                                |                                                 |    |  |  |

|   | 5.2              | Checking the Validity of the Compact Model                     |                                                 |    |  |  |

|   |                  | when its Parameters vary with the Source and Drain Voltages    |                                                 |    |  |  |

|   |                  | 5.2.1                                                          | E.K.V Parameter Identification (MATLAB          | 57 |  |  |

|   |                  | 0.2.1                                                          | IdentifDemo.m)                                  | 70 |  |  |

|   |                  | 5.2.2                                                          | How to Introduce Mobility Degradation?          |    |  |  |

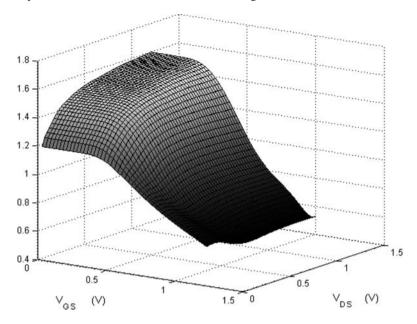

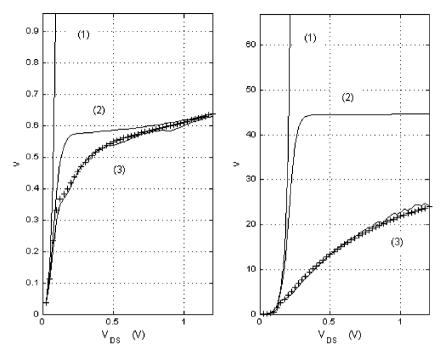

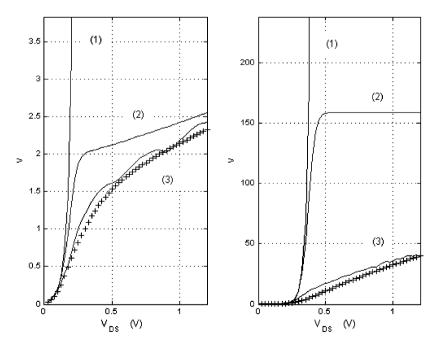

|   |                  | 5.2.3                                                          | Drain Current Reconstruction                    |    |  |  |

|   |                  |                                                                |                                                 |    |  |  |

Contents xiii

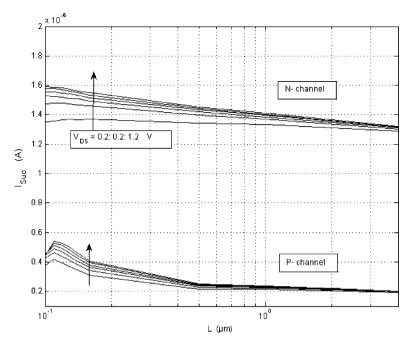

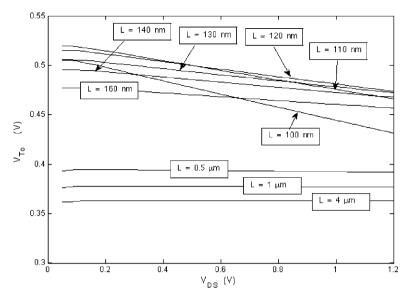

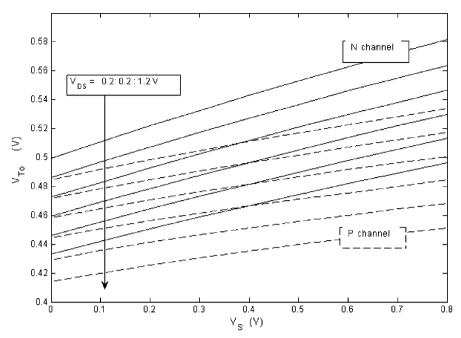

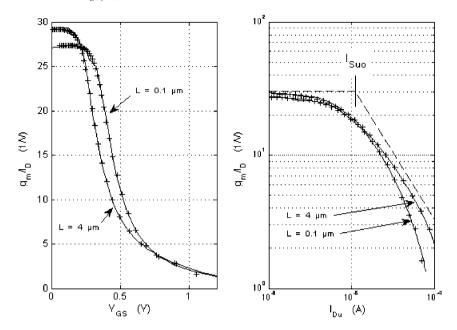

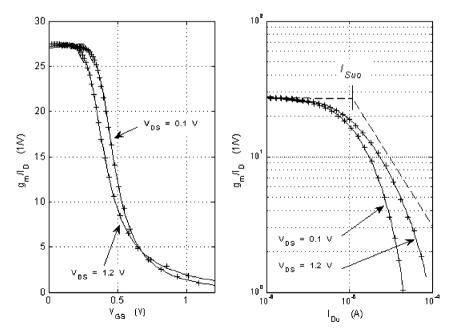

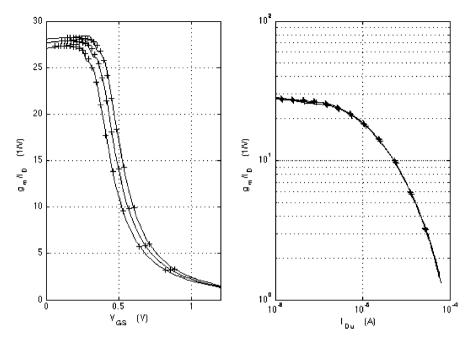

|   | 5.3   | Compa     | act Model Parameters Versus Bias and Gate Length   | 76  |

|---|-------|-----------|----------------------------------------------------|-----|

|   |       | 5.3.1     | The Influence of the Gate Length                   |     |

|   |       |           | on the Model Parameters                            | 76  |

|   |       | 5.3.2     | The Influence of Bias Conditions on the Parameters | 78  |

|   | 5.4   |           | structing $I_D(V_{DS})$ Characteristic             |     |

|   | 5.5   | Evalua    | tion of $g_x/I_D$ Ratios                           | 84  |

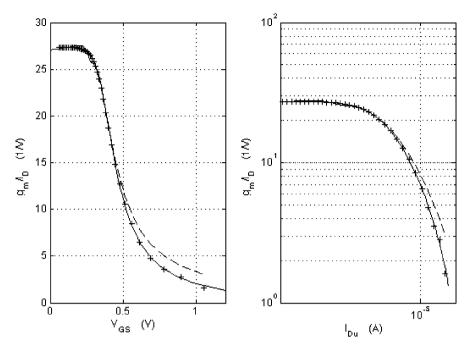

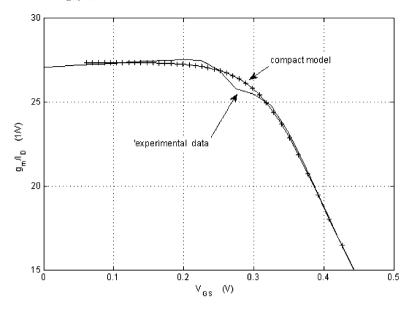

|   |       | 5.5.1     | The $g_m/I_D$ Ratio                                | 85  |

|   |       | 5.5.2     | The $g_d/I_D$ Ratio                                | 88  |

|   | 5.6   | Conclu    | isions                                             | 91  |

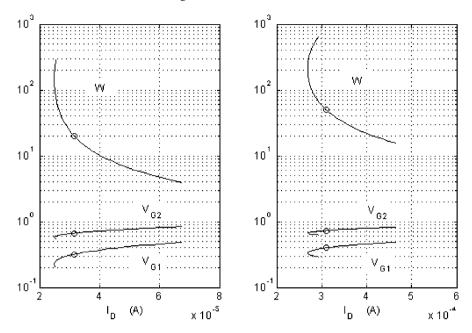

| 6 | The F | Real Intr | rinsic Gain Stage                                  | 93  |

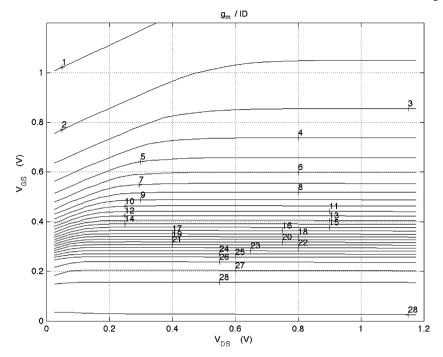

|   | 6.1   |           | ependence on Bias Conditions of the $g_m/I_D$      |     |

|   |       | and $g_d$ | /I <sub>D</sub> Ratios (MATLAB fig061.m)           | 93  |

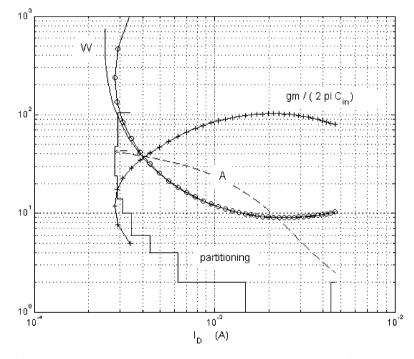

|   | 6.2   | Sizing    | the I.G.S with 'Semi-empirical' Data               | 94  |

|   |       | 6.2.1     | Sizing the I.G.S Loaded by a Constant Total        |     |

|   |       |           | Capacitance                                        | 95  |

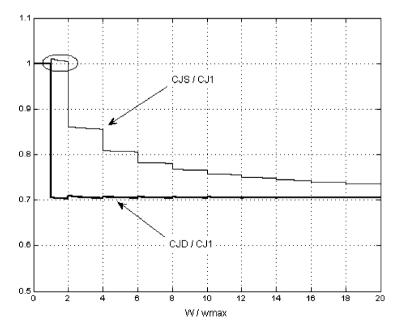

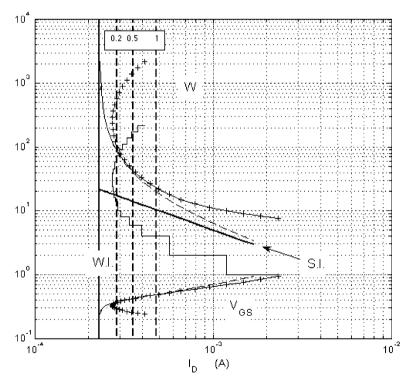

|   |       | 6.2.2     | Introduction of Extrinsic Capacitances             | 99  |

|   |       | 6.2.3     | Sizing the I.G.S Loaded by a Constant Load         |     |

|   |       |           | Capacitance                                        | 103 |

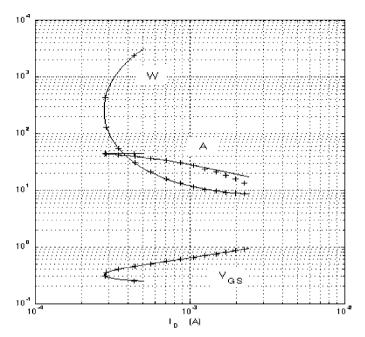

|   | 6.3   | Model     | Driven Sizing of the I.G.S.                        | 104 |

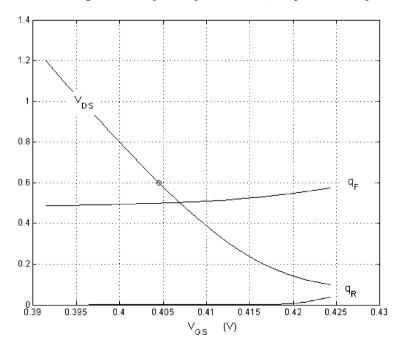

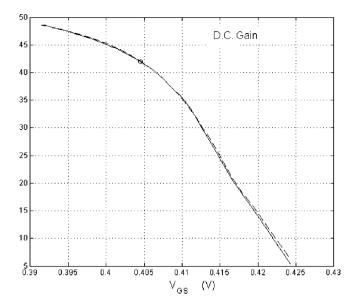

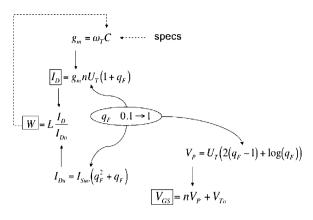

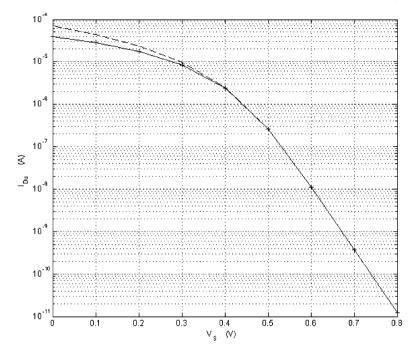

|   |       | 6.3.1     | Sizing W and ID (MATLAB fig612.m)                  | 104 |

|   |       | 6.3.2     | Evaluation of the Intrinsic Gain (MATLAB fig613.m) | 106 |

|   |       | 6.3.3     | An Alternative Method to Evaluate the Gain         |     |

|   |       |           | (MATLAB fig615.m)                                  | 107 |

|   |       | 6.3.4     | A Simplified Sizing Procedure                      |     |

|   | 6.4   | Slew-R    | Rate Considerations                                | 111 |

|   | 6.5   | Conclu    | sions                                              | 112 |

| 7 |       |           | a-Gate Configuration                               | 113 |

|   | 7.1   |           | Current Versus Source-to-Substrate Voltage         |     |

|   |       |           | b fig071.m)                                        |     |

|   | 7.2   |           | ascoded Intrinsic Gain Stage                       |     |

|   |       | 7.2.1     | Sizing the Cascode (Matlab fig074.m)               |     |

|   |       | 7.2.2     | Gain Evaluation of the Cascode (MATLAB fig075.m)   | 117 |

|   |       | 7.2.3     | The Poles of the Cascode Circuit                   |     |

|   |       |           | (MATLAB fig075.m)                                  | 118 |

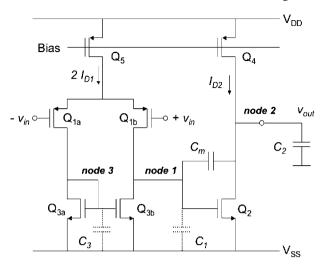

| 8 |       |           | ller Op. Amp.                                      |     |

|   | 8.1   |           | actory Considerations                              |     |

|   | 8.2   |           | iller Op. Amp                                      |     |

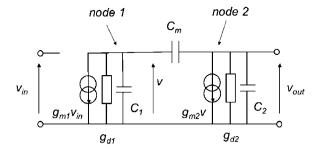

|   |       | 8.2.1     | Analysis of the Miller Operational Amplifier       |     |

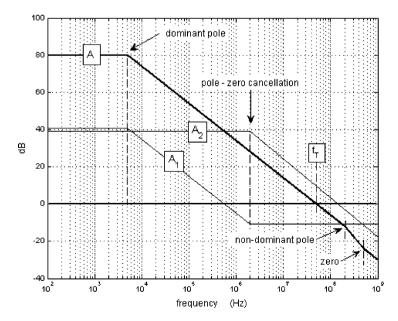

|   |       | 8.2.2     | Pole Splitting                                     |     |

|   |       | 8.2.3     | The Impact of the Current Mirror                   |     |

|   |       | 8.2.4     | Poles and Zeros                                    | 127 |

xiv Contents

| 8.3             | Sizing the Miller Operational Amplifier (MATLAB OpAmp.m).                 |      |  |  |  |

|-----------------|---------------------------------------------------------------------------|------|--|--|--|

|                 | 8.3.1 Sizing a Low-voltage Miller Op. Amp                                 | 130  |  |  |  |

|                 | 8.3.2 Sizing a High-Frequency Low-Power Miller                            | 1.40 |  |  |  |

| 0.4             | Op. Amp.                                                                  |      |  |  |  |

| 8.4             | Conclusion                                                                | 142  |  |  |  |

| Annex 1         | How to Utilize the Data available under 'extras.springer.com'             | 143  |  |  |  |

| A1.1            | Global Variables                                                          | 143  |  |  |  |

| A1.2            | An Example Making Use of the 'Semi-empirical' Data:                       |      |  |  |  |

|                 | The Evaluation of Drain Currents and g <sub>m</sub> /I <sub>D</sub> Ratio |      |  |  |  |

|                 | Matrices (MATLAB A12.m)                                                   | 144  |  |  |  |

| A1.3            | An Example Making Use of the E.K.V Global                                 |      |  |  |  |

|                 | Variables: The Elaboration of an ID(VGS)                                  |      |  |  |  |

|                 | Characteristic (Matlab A13.m)                                             | 146  |  |  |  |

| Annex 2         | The 'MATLAB' Toolbox                                                      | 149  |  |  |  |

| A2.1            | Charge Sheet Model Files                                                  |      |  |  |  |

| 112.1           | A2.1.1 The <b>pMat(T,N,tox</b> ) Function                                 |      |  |  |  |

|                 | A2.1.2 The surfpot(p,V,VG) Function                                       |      |  |  |  |

|                 | A2.1.3 The <b>IDsh(p,VS,VD,VG)</b> Function                               |      |  |  |  |

| A2.2            | Compact Model Files.                                                      |      |  |  |  |

|                 | A2.2.1 The <b>Identif 3(Nb,tox,VFB,T)</b> Function                        |      |  |  |  |

|                 | A2.2.2 The <b>invq(z)</b> Function                                        |      |  |  |  |

|                 | A2.2.3 The ComS(VGS,VDS,VS,lg) Function                                   |      |  |  |  |

| A2.3            | Other Functions                                                           |      |  |  |  |

|                 | A2.3.1 The <b>jctCap(L,W,R,V)</b> Function                                |      |  |  |  |

|                 | A2.3.2 The <b>Gss(x,H)</b> Function                                       |      |  |  |  |

| A 2             | Temperature and Mismatch, from C.S.M. to E.K.V.                           | 155  |  |  |  |

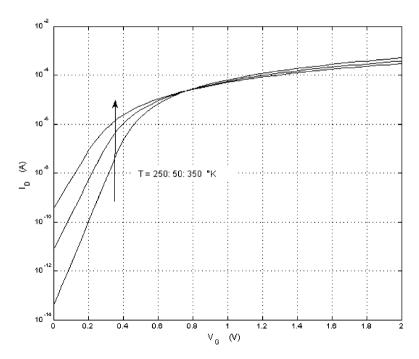

| Annex 3<br>A3.1 | The Influence of the Temperature on the Drain Current                     | 133  |  |  |  |

| A3.1            | (MATLAB A31.m)                                                            | 155  |  |  |  |

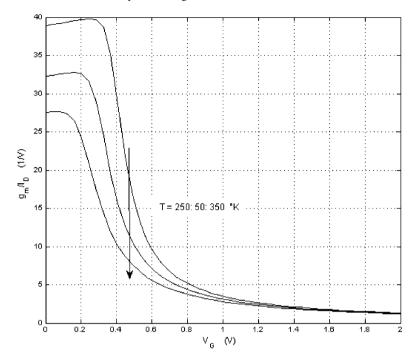

| A3.2            | The Influence of the Temperature on gm/ID (Matlab A32.m)                  |      |  |  |  |

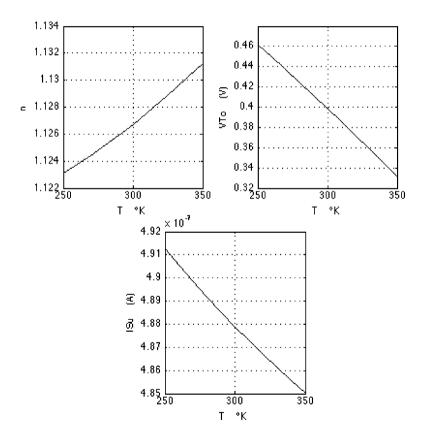

| A3.2            | Temperature Dependence of E.K.V Parameters                                | 150  |  |  |  |

| A3.3            | (MATLAB A33.m)                                                            | 159  |  |  |  |

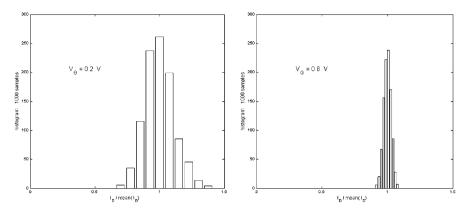

| A3.4            | The Impact of Technological Mismatches on the Drain                       | 150  |  |  |  |

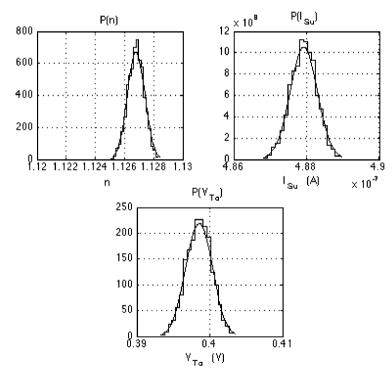

| A3.4            | Current (Matlab A34.m)                                                    | 150  |  |  |  |

| A3.5            | Mismatch and E.K.V Parameters (MATLAB A35.m)                              |      |  |  |  |

| A3.3            | Wishlatell and E.K. v Tarameters (WATEAD A33.iii)                         | 101  |  |  |  |

| Annex 4         | E.K.V. Intrinsic Capacitance Model                                        | 163  |  |  |  |

| Bibliogra       | Bibliography1                                                             |      |  |  |  |

| Index           |                                                                           | 169  |  |  |  |

#### **Notations**

$A, A_{DC}, A_{AC}$  voltage gain, DC and AC voltage gain

A.C.M. Advanced Compact Model C.L.M. Channel Length Modulation

C.S.M. Charge Sheet Model capacitor value

$C'_{ox}$  gate oxide capacitance per unit area

$C_{GB}$  gate-to-substrate capacitance  $C_{GD}$  gate-to-drain capacitance  $C_{GS}$  gate-to-source capacitance  $C_{I}$  junction capacitance

$C_{J_{SW}}$  peripheral side-wall junction capacitance  $C_{J_{SWg}}$  gate side-wall junction capacitance

C<sub>m</sub> Miller capacitance

CMOS Complementary MOS

D diffusion constant

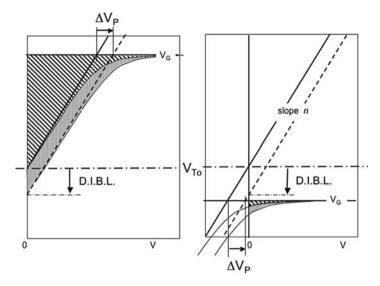

D.I.B.L. Drain Induced Barrier Lowering

E.K.V. Enz, Krumenacher and Vittoz compact model

G.V.O. Gate Voltage Overdrive voltage

$g_d$  output conductance  $g_m$  gate transconductance  $g_{mb}$  bulk transconductance  $g_{ms}$  source transconductance

$i, i_F, i_R$  normalized drain current, forward and reverse i

I.G.S. Intrinsic Gain Stage  $I_D$  DC drain current

$I_{Du}$  unary DC drain current (W = L)

$I_S$  specific current

$I_{Su}$  unary specific current (W = L)  $I_{Suo}$  weak inversion unary specific current

L gate length

N impurity concentration

n slope factor

xvi Notations

PolyN, PolyPmobility degradation polyn. of N- and P-channel transistors $q, q_F, q_R$ normalized mobile charge density, forward and reverse q $qs, q_D$ normalized mobile charge density at the source and drain

$Q_B'$  bulk charge density  $Q_i'$ , mobile charge density  $Q_t'$ , total charge density R.H.P. Right Half Plane zero

$S_{VTo}$  threshold voltage sensitivity factor with respect to  $V_{DS}$  mobility degradation function of N- and P-channel transistors

$U_T$  thermal voltage kT/q

V, I, v, i large and small signal voltage or current

$V_A$  Early voltage

$V_S$ ,  $V_G$ ,  $V_D$  source, gate and drain voltage with respect to substrate  $V_{GS}$ ,  $V_{DS}$  gate and drain voltage with respect to the source

$V_P, V_{PS}$  pinch-off voltage with respect to the substrate or the source

*v<sub>sat</sub>* saturation velocity of mobile carriers

$V_T$  threshold voltage with respect to the substrate  $V_{To}$  threshold voltage with respect to the source

W gate width

W.I, M.I, S.I weak, moderate and strong inversion  $\beta$   $\mu$ C'  $_{ox}$  W/L of MOS transistor gamma of SPICE program

$\mu$  mobility

$\mu_o$  low-field mobility  $\psi_S$  surface potential

$\omega$  angular frequency  $(2\pi f)$

$\omega_c$  angular cut-off frequency  $(2\pi f_c)$   $\omega_T$  angular transition frequency  $(2\pi f_T)$

## **Chapter 1 Sizing the Intrinsic Gain Stage**

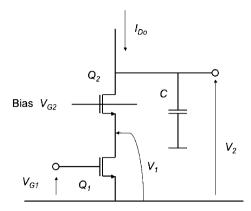

#### 1.1 The Intrinsic Gain Stage

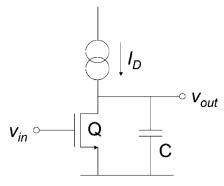

Sizing methods assessing drain currents and gate widths of a simple circuit are reviewed in this chapter. The circuit, shown in Fig. 1.1, consists of a saturated common source transistor loaded by a capacitor. A constant current source is feeding the drain. The circuit is called currently the 'Intrinsic Gain Stage' (I.G.S.), the name 'intrinsic' underlining the fact that few parts aside the transistor control the performances of the circuit.

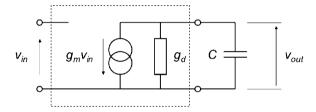

Our objective is to find gate widths and drain currents enabling to achieve a prescribed gain-bandwidth product  $\omega_T$ . We therefore consider the small signal equivalent circuit shown in Fig. 1.2. The input is an open circuit while the output consists of a dependent current source  $g_m v_{in}$  (where  $g_m$  represents the transconductance of Q) in parallel with the output conductance  $g_d$  and the capacitor C.

#### 1.2 The Intrinsic Gain Stage Frequency Response

We divide the I.G.S in high and low frequency sub-circuits to evaluate its frequency response. At high frequencies, all the current delivered by the current source flows through the capacitor for C behaves like a short with respect to the output resistance. Hence:

$$g_m v_{in} = -j\omega C v_{out} \tag{1.1}$$

The AC gain is given consequently by:

$$A_{AC} = -\frac{\left(\frac{g_m}{C}\right)}{j\omega} \tag{1.2}$$

At low frequencies, the opposite takes place. The capacitor C is practically an open circuit so that the current flows through the output conductance  $g_d$ . Hence:

$$g_m v_{in} = -g_d v_{out} (1.3)$$

1

**Fig. 1.1** The 'Intrinsic Gain Stage'

Q is a saturated transistor

Fig. 1.2 The equivalent small signal circuit of the 'Intrinsic Gain Stage'

The DC gain is given by:

$$A_{DC} = -\frac{g_m}{g_d} \tag{1.4}$$

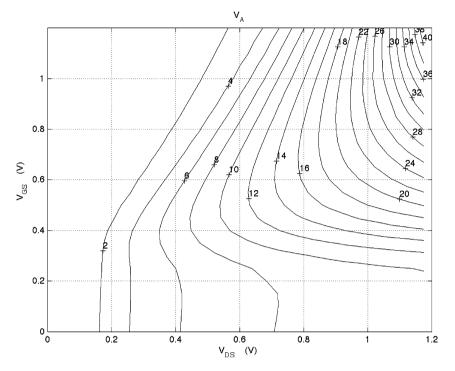

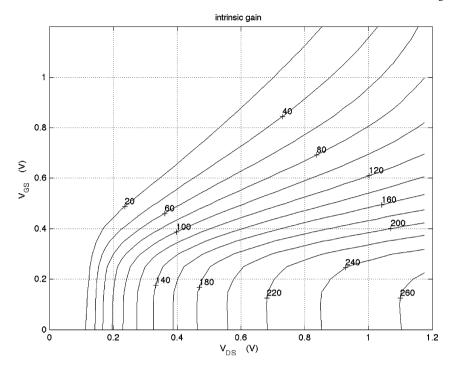

To get closer to real world transistors, we are going to take into consideration the dependence on bias conditions of the output conductance  $g_d$ . Generally, the impact of the current on  $g_d$  is acknowledged by replacing the output conductance by the ratio of the drain current over the so-called Early voltage  $V_A$ . The Early voltage is supposed to be constant, which implies that all  $I_D(V_D)$  characteristics cross the horizontal axis at a unique point once extrapolated. While more or less correct in weak inversion, <sup>1</sup> this is a rather crude approximation in strong inversion, particularly with sub-micron transistors. Our goal being presently to lay down the grass roots of sizing, we are going to assume nevertheless that  $V_A$  is constant and postpone more advanced representations to later chapters. Equation 1.4 may be rewritten then as follows:

$$A_{DC} = -\frac{g_m}{I_D} V_A \tag{1.5}$$

<sup>&</sup>lt;sup>1</sup> Weak inversion occurs when MOS transistors are biased with gate voltages lower than the threshold voltage resulting in an exponential relationship between drain current and gate voltage (Vittoz 1977). Strong inversion designates the region where the classic quadratic current to voltage relationship holds true. The transition from weak to strong inversion is currently referred to as the moderate inversion region. This region plays a key role in CMOS analog circuits.

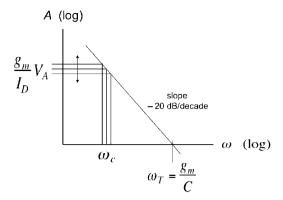

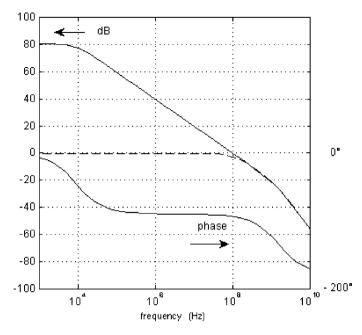

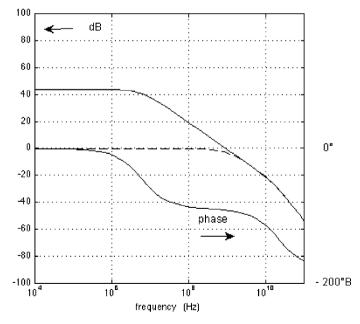

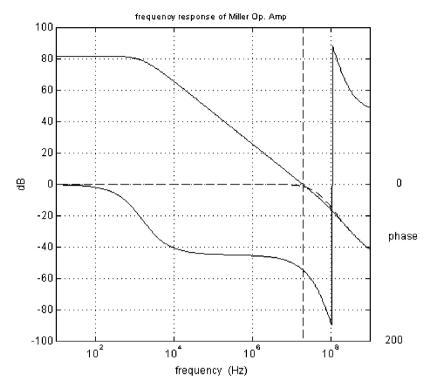

**Fig. 1.3** The frequency response of the Intrinsic Gain Stage

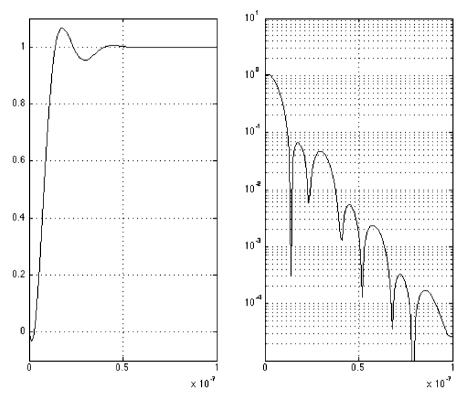

Figure 1.3 shows the frequency response of the Intrinsic Gain Stage according to Eq. 1.5 for the low frequency part and according to Eq. 1.2 for the high frequency part.

The point where the two asymptotes cross each other  $\omega_c$  is called currently the *cut-off angular frequency* and the point  $\omega_T$  where the high frequency response crosses the horizontal axis (the 0 dB gain point) the *transition angular frequency*:

$$\omega_T = \frac{g_m}{C} \tag{1.6}$$

The name *gain-bandwidth product* is given also to the transition angular frequency for  $\omega_T$  is equal to  $\omega_c$  times the gain since the Intrinsic Gain Stage is a true first order system.  $\omega_T$  is a more significant landmark than  $\omega_C$  for it characterizes the high frequency behavior of the I.G.S. without the need to know highly unpredictable Early voltages.

#### 1.3 Sizing the Intrinsic Gain Stage

How can one fix the drain current and aspect ratio W/L of the I.G.S so as to achieve a desired *transition frequency*  $f_T$ ? As far as the transconductance, there is no choice for Eq. 1.6 fixes already  $g_m$ :

$$g_m = \omega_T C = 2\pi f_T C \tag{1.7}$$

The problem boils down consequently to find means to connect the drain current  $I_D$  and the W/L ratio to the transconductance  $g_m$ . A large signal model of the transistor is needed therefore. The first that comes up of course is the classical quadratic MOS model.

#### 1.3.1 Sizing the I.G.S. with the Quadratic Model

The drain current of saturated MOS transistors is given by the well-known quadratic expression:

$$I_D = \beta \; \frac{(V_G - V_{th})^2}{2 \, n} \tag{1.8}$$

$V_{th}$  being the threshold voltage, while

$$\beta = \mu \, C_{ox}' \frac{W}{L} \tag{1.9}$$

where

$\mu$  is the mobility of the mobile carries of the channel

$C'_{ox}$  the gate oxide capacitance per unit-area (the ' meaning capacitance per unit-area)

W and L respectively the gate width and length

the slope factor generally comprised between 1.2 and 1.5

The derivative of  $I_D$  with respect to  $V_G$  yields the transconductance  $g_m$ :

$$g_m = \frac{\partial I_D}{\partial V_G} = \beta \, \frac{V_G - V_{th}}{n} = \sqrt{\frac{2\beta I_D}{n}} \tag{1.10}$$

W/L and  $I_D$  are connected thus to the gain-bandwidth product through  $g_m$ . Combining Eqs. 1.9 and 1.10, one has:

$$\frac{W}{L} = \frac{ng_m^2}{2\mu C_{ox}'} \cdot \frac{1}{I_D} \tag{1.11}$$

Instead of a single  $I_D$  and W/L, many doublets achieve the desired gain-bandwidth product. We can put forward thus additional objectives, like a large DC gain. Since according to Eq. 1.5 the gain varies like the reciprocal of the drain current, the smaller the drain current, the larger the gain. Not only the gain increases, but the power consumption lessens in the same time. Something is wrong however for zero drain current is supposed to entail infinite gain! In fact, as the current is getting smaller, the transistor enters successively in moderate and weak inversion. The quadratic model does not represent the drain current anymore. Another model is required.

#### 1.3.2 Sizing the I.G.S. by Means of the Weak Inversion Model

In weak inversion, the drain current can be represented by means of an exponential expression (Vittoz 1977):

$$I_D = I_o \exp\left(\frac{V_G}{nU_T}\right) \tag{1.12}$$

The transconductance is given then by:

$$g_m = \frac{I_D}{nU_T} \tag{1.13}$$

where  $U_T$  stands for kT/q and k for the Boltzmann constant. To attain the desired  $\omega_T$ , the drain current must be equal to:

$$I_{D \min} = nU_T g_m \tag{1.14}$$

This is a very different result from what we got in strong inversion. The drain current alone fixes the gain-bandwidth product while the aspect ratio has no influence at all. The outcome recalls bipolar transistors for their transition frequency also depends on the collector current only and not on the emitter size (as long as strong injection does not take place of course). MOS transistors in weak inversion and bipolar transistors share indeed a common feature: their currents are mainly diffusion currents.

#### 1.3.3 Sizing the I.G.S. in the Moderate Inversion Region

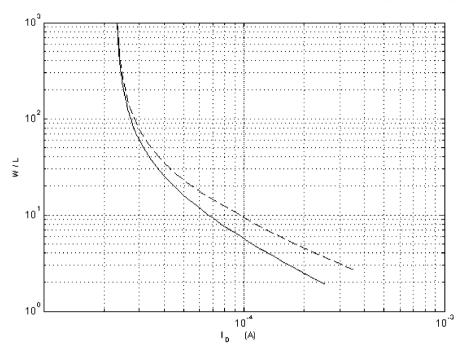

Sizing in moderate inversion requires a better model. A good candidate is the compact model introduced in Chapter 4, which leads to the expression below demonstrated in Section 4.7:

$$\frac{W}{L} = \frac{ng_m^2}{2\mu \, C'_{ox}} \frac{1}{I_D - I_{D\,\text{min}}} \tag{1.15}$$

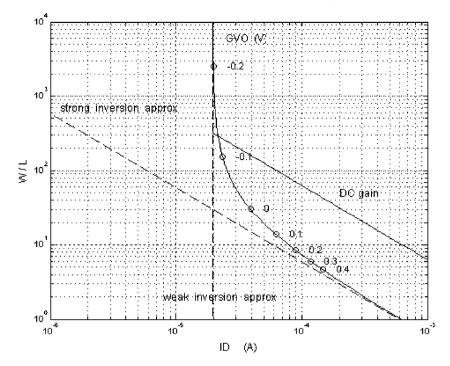

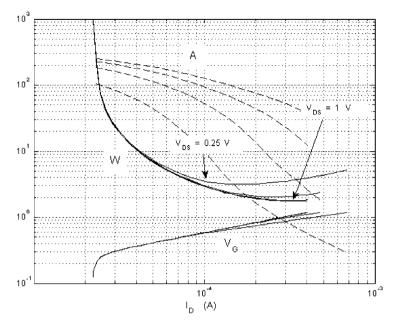

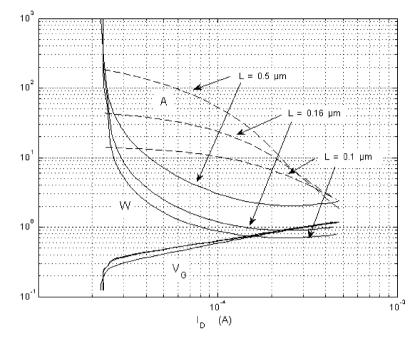

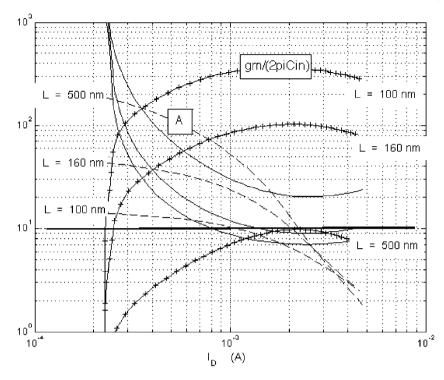

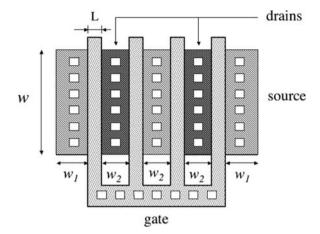

The expression is valid in all modes of operation, from strong to weak inversion. Suppose we want to design an Intrinsic Gain Stage loaded by a 1 pF capacitor targeting a transition frequency of 100 MHz. The transistor's  $\mu C'_{ox}$  and slope factor n are respectively equal to  $4\times 10^{-4}$  A.V<sup>-2</sup> and 1.2. Figure 1.4 displays the aspect ratios versus drain current achieving the desired gain-bandwidth product. The result is compared to the strong and weak inversion approximations considered earlier. Below  $I_{Dmin}$ , nearly 20  $\mu$ A, it is impossible to achieve the desired gain-bandwidth product. Above, W/L's conform to a hyperbolic curve whose asymptotes coincide with the strong and weak inversion approximations. But in moderate inversion, large differences are clearly visible with respect to the strong and weak inversion approximations.

The same figure displays also the AC gain predicted by Eq. 1.5 considering an Early voltage of 10 V. Since the gain varies like the reciprocal of  $I_D$ , small drain currents mean large gains. When the drain current reaches the minimum given

**Fig. 1.4** Aspect ratio W/L and AC gain versus the drain current, of an (ideal) Intrinsic Gain Stage aiming at a transition frequency of 100 MHz with a load capacitance of 1 pF. The Early voltage is assumed to be constant and equal to 10. Circles display the difference between gate and threshold voltages, the so-called *Gate Voltage Overdrive* (GVO) (MATLAB fig014.m)

by Eq. 1.14, the gain is largest and equal to the expression below obtained after combining Eqs. 1.5 and 1.13:

$$A_{AC \max} = -\frac{V_A}{nU_T} \tag{1.16}$$

Since the thermal voltage  $U_T$  at room temperature is only 26 mV, very large gains can be obtained depending on  $V_A$ . This once again stresses the commonality shared by bipolar transistors and MOS transistors in weak inversion. The only difference is the n factor. With bipolar transistors, the slope factor is equal to one.

Moderate inversion offers interesting compromises. Currents are smaller than in strong inversion while the W/L ratios are more acceptable than in weak inversion. Gains moreover are only slightly lesser than in weak inversion. Moderate inversion however brings about some drawbacks also. The larger widths that are needed entail more parasitic capacitances than in strong inversion. These require enhancing transconductances, thus also the drain currents, one of the reasons designers kept away from moderate inversion for a long time until the advent of short channel devices.

Where lies the boundary between moderate and strong inversion? To answer the question, consider the  $(V_G - V_{th})$  difference, called also the *Gate Voltage Overdrive* (G.V.O.). According to (Lak 1994) strong inversion takes place as soon as the gate voltage overdrive (marked by circles in Fig. 1.4) exceeds 0.2 V. When this happens, moderate inversion W/L's coincide practically with the strong inversion asymptote. Where does weak inversion start? A clear limit is harder to trace, but the fast increase of W/L once the current approaches  $I_{Dmin}$  is clearly a sign that weak inversion is taking place. More rigorous limits will be proposed in Chapter 4 when the compact model is introduced.

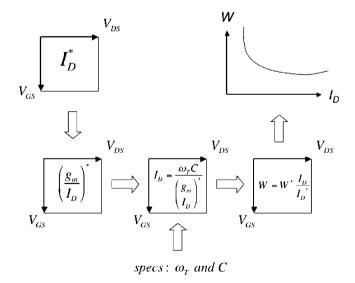

#### 1.4 The $g_m/I_D$ Sizing Methodology

The transconductance over drain current ratio is a resourceful tool for performing sizing. The method exploits the fact that transconductances and drain currents vary like the gate width (as long as the widths are large enough to avoid border effects of course). Because the  $g_m/I_D$  ratio doesn't depend on the gate width, drain currents achieving any prescribed gain-bandwidth product can be derived from the expression below where the numerator is the transconductance given by Eq. 1.7 and the denominator the transistor's  $g_m/I_D$  ratio derived from a similar device whose gate width  $W^*$  and gate length  $L^*$  are known:

$$I_D = \frac{g_m}{\left(\frac{g_m}{I_D}\right)^*} \tag{1.17}$$

Knowing the drain currents, widths follow from the proportionality:

$$W = (W)^* \frac{I_D}{(I_D)^*} \tag{1.18}$$

Equations 1.17 and 1.18 form a set of parametric equations that determines drain currents and gate widths achieving the gain-bandwidth product fixed by  $g_m$ .<sup>3</sup> The key of the sizing methodology is the denominator of Eq. 1.17, for it plays the role of a parameter enabling to sweep the transistor through all modes of operation. It is actually the slope of the drain current characteristic plotted versus the gate voltage in semilog axes, for:

$$\left(\frac{g_m}{I_D}\right)^* = \frac{1}{I_D^*} \frac{dI_D^*}{dV_G} = \frac{d}{dV_G} \log\left(I_D^*\right) \tag{1.19}$$

<sup>&</sup>lt;sup>2</sup> The gm/ID sizing methodology was introduced for the first time by the paper of (Silveira et al. 1996). Since then, the concept is referred to in many publication (Binkley et al. 2003; Binkley 2007) and (Girardi et al. 2006).

$<sup>^3</sup>$  When  $I_D$  and  $g_m$  are interchanged, sizing is aiming at slew-rate instead of the gain-bandwidth product.

In weak inversion, the slope of the drain current characteristic is large and practically constant. The currents derived from Eq. 1.17 are the smallest currents fulfilling the gain-bandwidth specifications. As we move towards strong inversion the slope decreases so that larger currents are needed to meet the gain-bandwidth specification.

The question is how to set up the denominator of Eq. 1.17? Two issues lie for the hand: experimental or analytical. The first makes use of Eq. 1.19 and derives the transconductance over drain current ratio from experimental  $I_D(V_{GS})$  characteristics. The currents stored in look-up tables are the result of measurements carried out on real transistors whose width  $W^*$  and gate length  $L^*$  are known a priori. The drain currents may be derived also from advanced models such as BSIM or PSP4 for these allow reconstructing drain currents that are very close to real drain currents. We call this the semi-empirical  $g_m/I_D$  sizing method. The other method, the model-driven method, makes use of analytical expressions for  $(g_m/I_D)^*$ . It requires having at one's disposal an accurate large signal model that lends itself to analytical expressions. The basic E.K.V. model introduced in Chapter 4 leads to analytic expressions of the transconductance over drain current ratio. Unfortunately, it is not a good candidate for it is too basic to take into consideration important second order effects like threshold voltage roll-off, D.I.B.L, gate length modulation etc that plague real MOS transistors. More elaborated version of the E.K.V. model (Enz and Vittoz 2006) do take care of these but evade chances to take advantage of analytic expressions owing to the large number of parameters and expressions they require. The semi-empirical method does not suffer of this drawback of course.

Yet, a simple model taking care of second order effects would be an asset. Further in this book, we show that when its parameters are not constant but vary with bias conditions and gate lengths, the basic E.K.V. model can be a good candidate nevertheless for model-driven sizing. Though the model itself ignores second order effects, the parameters reflect their impact. What makes this method attractive is the fact that analytic expressions offer sensible manners to control the mode of operation of the transistors, whereas the semi-empirical method proceeds blindly.

#### 1.5 Conclusions

In this introductory chapter, we review the basics of sizing CMOS analog circuits. The transconductance over drain current ratio<sup>5</sup> offers a an interesting alternative for:

<sup>&</sup>lt;sup>4</sup> BSIM is a widely used state-of-the-art model that is available in the public domain, see [BSIM]. It is based on threshold voltage formulations and this may explain some weaknesses in moderate inversion.

PSP for Penn State University and Philips (now NXP) is considered to be the more accurate industrial standard available nowadays (PSP 2006). It is based on the surface potential model (like the Charge Sheet Model).

<sup>&</sup>lt;sup>5</sup> The method can be extended to other (trans)conductances. When the numerator and denominator of Eq. 1.17 are replaced respectively by  $g_d$  and  $g_d/I_D$ , the algorithm performs sizing in view of the output conductance.

1.5 Conclusions 9

•  $g_m/I_D$  is a technological attribute bridging the transconductance, a small signal quantity, to the drain current, a large signal quantity. As soon one is fixed, the other follows.

- The  $g_m/I_D$  ratio controls gain and power consumption, the larger  $g_m/I_D$ , the smaller the drain current and the larger the gain.

- The  $g_m/I_D$  sizing methodology applies however only as long as the widths are large enough to ignore lateral effects, a condition that holds true with most CMOS analog circuits.

Two approaches are possible: semi-empirical or model-driven. The first takes advantage of real measurements or data derived from advanced MOS models. The second makes use of models supposed to be accurate and simple enough to pave the way towards reliable analytical expressions of the transconductance over drain current ratios. Unfortunately no such model exists, except the basic E.K.V. model when its parameters are allowed to vary with bias conditions and gate lengths. We show further that the results are comparable to those obtained by means of the semi-empirical method.

## **Chapter 2 The Charge Sheet Model Revisited**

#### 2.1 Why the Charge Sheet Model?

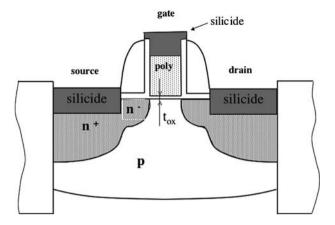

We review in this chapter the main attributes of the 'Charge Sheet Model' (C.S.M.) introduced by J.R. Brews in 1978 (Brews 1978; Van de Wiele 1979). Although its name contains the word 'Model', the C.S.M is not a design tool. It is an invaluable means however for understanding some of the mechanisms governing current in MOS transistors for it scrutenizes phenomena otherwise difficult to apprehend. Unfortunately, the C.S.M. concerns only long channel MOS transistors implemented in a uniformly doped substrate (gradual channel approximation). Trying to predict drain currents of real transistors with the C.S.M. does not work.

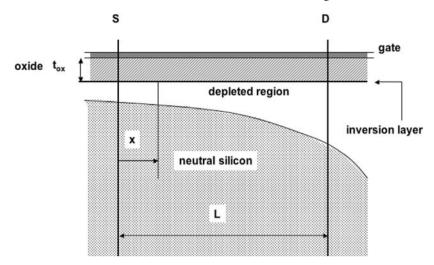

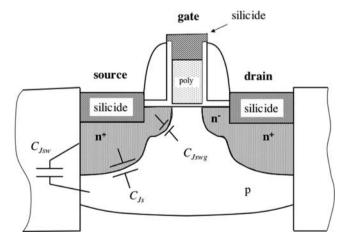

Figure 2.1 depicts the structure of the NMOS transistor considered throughout this chapter. The two vertical lines without any other demarcation called respectively S and D symbolize the source and drain junctions. Two-dimensional effects are ignored, obliterating consequently items such as channel length modulation, Drain Induced Barrier Lowering (DIBL), etc. The source, drain and gate voltages are called respectively  $V_S$ ,  $V_D$  and  $V_G$ , the surface potential  $\psi_S$  and the nonequilibrium voltage V. The latter, called also the channel voltage, varies from  $V_S$  at the source to  $V_D$  at the drain. Single indices relate to voltages defined with respect to the substrate. Double indices relate to voltage defined with respect to references other than the substrate. For instance,  $V_{GS}$  is the voltage difference between the gate and the source.

#### 2.2 The Generic Drain Current Equation

Current in MOS transistors results from mobile carries moving in the channel. It can be represented by the expression below where W is the width of the transistor and  $Q'_i$  the mobile charge density along the channel:

$$I_D = W \cdot (-Q_i') \cdot velocity \tag{2.1}$$

$<sup>^{1}</sup>$  V is the difference between the "quasi Fermi level" of electrons in the inversion layer and the "quasi Fermi level" of holes in the substrate.

Fig. 2.1 The gradual channel MOS transistor

Two transport mechanisms are taking place currently: *drift* and *diffusion*. The *drift current* velocity is supposed to be proportional to the electrical field E:

$$drift \ current \ velocity = -\mu \ E \tag{2.2}$$

The *mobility coefficient*  $\mu$  is assumed to be constant generally. This is correct as long as electrical fields do not exceed some limit. Modern transistors face very large fields for their gate lengths are ever shorter while supply voltages don't scale down necessarily at the same rate. As electrical fields are getting larger, the velocity of the carriers starts to slow down so that mobility declines. The effect can be taken into account by making  $\mu$  a function of the electrical field.

The *diffusion current* is governed by the non-uniform concentration of carriers (like gas scattering in a closed vessel to homogenize the pressure). The diffusion current velocity is supposed to be proportional to the carrier's concentration:

diffusion current velocity =

$$-D\frac{1}{n}\frac{\partial n}{\partial x} = -D\frac{1}{Q_i'}\frac{\partial Q_i'}{\partial x}$$

(2.3)

The diffusion constant D is related to the mobility  $\mu$  by the Einstein relation:

$$D = \mu U_T \tag{2.4}$$

As the electrical field along the channel is replaced by the derivative of the surface potential  $\psi_S$ :

$$E = -\frac{d\psi_S}{dx} \tag{2.5}$$

Equation 2.1 can be rewritten as follows:

$$I_D = \mu W \left[ -Q_i' \frac{d\psi_S}{dx} + U_T \frac{dQ_i'}{dx} \right]$$

(2.6)

or:

$$I_D dx = \mu W \left[ -Q_i' d\psi_S + U_T dQ_i' \right]$$

(2.7)

While the left side of the above equation lends itself to integration (current is constant along the channel), the right part doesn't. One of the two integration variables should be expressed as a function of the other. Two strategies are possible. In the Charge Sheet Model, the charge density is expressed as a function of the surface potential. In the compact model, discussed in Chapter 4, the surface potential is expressed as a function of the charge density. The first representation follows a rigorous treatment while the second implies an approximation. The first does not lend itself to circuit design, the second does.

#### 2.3 The Charge Sheet Model Drain Current Equation

In this chapter, we lay down the grounds of the Charge Sheet Model. We take the surface potential as integration variable rewriting the right part of Eq. 2.7 as shown below after introducing the gate oxide capacitance per unit-area  $C'_{ox}$ :

$$I_D dx = \mu C'_{ox} W \left[ -\frac{Q'_i}{C'_{ox}} + U_T \frac{d}{d\psi_S} \left( \frac{Q'_i}{C'_{ox}} \right) \right] d\psi_S$$

(2.8)

To perform the integration, an expression of  $Q'_i/C'_{ox}$  versus the surface potential is required. The equation is derived currently from the total charge density  $Q_t/C'_{ox}$  expression obtained after combining the Gauss law, the Poisson equation and Boltzmann statistics (detailed computations can be found in textbooks):

$$-\frac{Q_t'}{C_{or}'} = \gamma \cdot \left[ U_T \exp\left(\frac{\psi_S - 2\phi_B - V}{U_T}\right) + \psi_S \right]^{1/2}$$

(2.9)

where:

V represents the non-equilibrium voltage along the channel

$\Phi_B$  is the bulk potential, depending on the ratio of the substrate doping concentration N over the intrinsic carrier density of silicon  $n_i$

$$\phi_B = U_T \log \left( \frac{N}{n_i} \right) \tag{2.10}$$

$\gamma$  is the Gamma commonly used in SPICE, which depends on N and the oxide thickness via the oxide capacitance  $C'_{ox}$ :

$$\gamma = \frac{1}{C'_{ox}} \sqrt{2 \, q \, \varepsilon_{\rm S} \, N} \tag{2.11}$$

where q is the electron charge,

$\varepsilon_{\rm S}$  the silicon permittivity

N the substrate impurity concentration

The two terms under the square root of Eq. 2.9 relate respectively to the inversion charge density (left term) and the depleted charge density (right term). If we ignore the first term, in other words if the mobile charge density  $Q_i'$  vanishes, the total charge density  $Q_i'$  resumes to the fixed charge density  $Q_i'$  so that what remains of Eq. 2.9 boils down to:

$$-\frac{Q_b'}{C_{cr}'} = \gamma \sqrt{\psi_S} \tag{2.12}$$

An expression of the mobile carrier's density lies now for the hand. We start from the Gauss law<sup>2</sup>:

$$V_G = -\frac{Q_t'}{C_{t...}'} + \psi_S \tag{2.13}$$

Since  $Q_t'$  is the sum of mobile and fixed charge densities, we may write owing to Eq. 2.12:

$$V_G = -\frac{Q_i'}{C_{ox}'} + \gamma \sqrt{\psi_S} + \psi_S \tag{2.14}$$

which leads to the expression of  $Q'_i/C'_{ox}$  versus the surface potential that we are looking for:

$$-\frac{Q_i'}{C_{ox}'} = V_G - \gamma \sqrt{\psi_S} - \psi_S \tag{2.15}$$

We can evaluate now the derivative with respect to the surface potential of  $Q'_i/C'_{ox}$ :

$$d\left(-\frac{Q_i'}{C_{oc}'}\right) = -\left(1 + \frac{\gamma}{2\sqrt{\psi_S}}\right)d\psi_S \tag{2.16}$$

and combine Eqs. 2.8, 2.15 and 2.16 to get the differential equation below ready for integration:

$$I_D dx = \mu C'_{ox} W \cdot \left[ V_G - \gamma \sqrt{\psi_S} - \psi_S + U_T \left( 1 + \frac{\gamma}{2\sqrt{\psi_S}} \right) \right] d\psi_S \qquad (2.17)$$

$<sup>^2</sup>$  The contact potentials between the gate material, the substrate material and the metal connections as well as the fixed charges trapped in the oxide produce a shift of the gate voltage that can be taken into account by adding to the gate voltage a constant voltage, called the Flat Band Voltage  $V_{FB}$ .

After integration, the expression of the drain current below is found where  $\psi_{SD}$  and  $\psi_{SS}$  represent respectively the surface potential at the drain and the source and  $\beta$  as usual  $\mu C'_{ox}W/L$ :

$$I_D = \beta \left[ F(\psi_{SD}) - F(\psi_{SS}) \right] \tag{2.18}$$

with the function  $F(\psi_S)$  given by:

$$F(\psi_S) = -\frac{1}{2}\psi_S^2 - \frac{2}{3}\gamma \,\psi_S^{1.5} + (V_G + U_T) \,\psi_S + \gamma \,U_T \psi_S^{0.5} \eqno(2.19)$$

Equations 2.18 and 2.19 are interesting and frustrating results in the same time. The good news is that the drain current can be expressed as a polynomial of the square root of the surface potential. The bad news is that we must find a way to connect the source and drain surface potentials  $\psi_{SS}$  and  $\psi_{SD}$  to  $V_S$  and  $V_D$ . No analytical expression is available. The only way out is to extract the surface potential from the expression below resulting from the combination of Eqs. 2.13 and 2.9.

$$V_G = \gamma \cdot \left[ U_T \exp\left(\frac{\psi_S - 2\phi_B - V}{U_T}\right) + \psi_S \right]^{1/2} + \psi_S$$

(2.20)

Since Eq. 2.20 is an implicit non-linear equation of  $\psi_S$ , the evaluation must be done numerically. The MATLAB function *surfpot* residing in the Matlab toolbox under 'extras.springer.com' takes care of this. For more details, please consult Annex 2.

#### 2.4 Common Source Characteristics

The analytical expression of the drain current given by Eqs. 2.18 and 2.19 together with the *surfpot* function solving Eq. 2.20 pave the road towards experiments that help understanding the behavior of MOS transistors under low-power low-voltage conditions. Some examples are reviewed in the next sections considering an N-channel transistor implemented in a substrate having an impurity concentration equal to  $10^{17}$  atoms cm<sup>-3</sup> and an oxide thickness equal to 5 nm. The flat-band voltage  $V_{FB}$  is supposed to be equal to 0.6 V and the temperature equal to be 300 K. The reader can make use of the toolbox to run additional 'experiments', like those of Annex 3, which examine the impact of technology and temperature on transistor's performances.

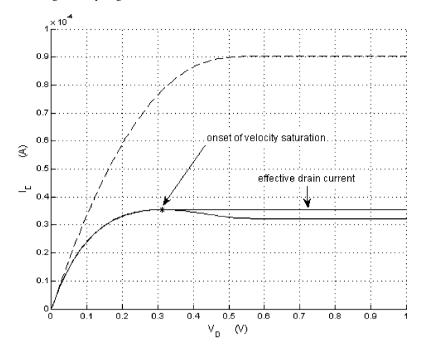

#### 2.4.1 The $I_D(V_D)$ Characteristics

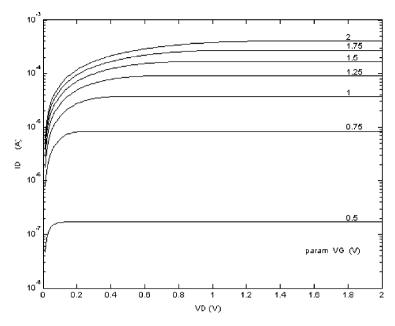

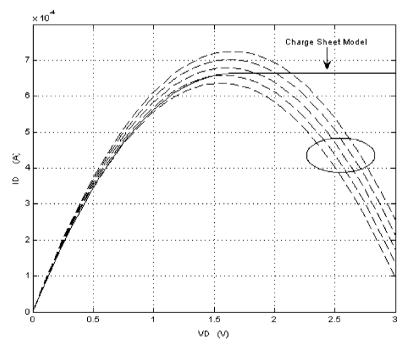

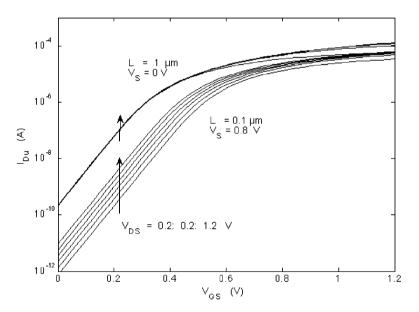

The curves displayed in Fig. 2.2 show drain currents versus the drain voltage characteristics obtained by means of the program below making use of two additional MATLAB function, pMat and IDsh, reported in the toolbox. The unusual semilog

Fig. 2.2 Drain current versus drain voltage obtained by means of the *IDsh* file (MATLAB fig022.m)

vertical scale used for the display is chosen in order to plot drain currents from weak to strong inversion in a single diagram encompassing five orders of magnitude.

```

clear

clf

% data techno

T = 300;

N = 1e17;

tox = 5;

VFB = .6;

% compute pMat(technology vector)

p = pMat(T, N, tox);

% compute ID (VD)

VS = 0;

M = 201; VD = linspace(.01, 2, M).';

UG = linspace (2, .5, 7);

for k = 1: length(UG),

ID(:,k) = IDsh(p,VS,VD,UG(1,k) + VFB);

end

% plot

semilogy(VD,ID,'k'); axis([0 2 1e-8 1e-3]);

```

A series of well-known facts are clearly visible:

- The Charge Sheet Model represents drain currents in a smooth way all over the so-called linear (resistive) and saturated modes of operation. The model is 'continuous'. In other words it does not require several equations to describe distinct modes of operation.

- 2. The passage from strong to weak inversion and vice versa is gradual and continuous too.

- 3. The distances between adjacent  $I_D(V_D)$  characteristics gets larger as one goes from strong to weak inversion. Since all gate voltage increments are identical, the transconductance over drain current ratio is larger in weak than in strong inversion (remind weak and moderate inversion conditions achieve better gains).

- 4. The pinch-off voltage is very small in weak inversion and remains quasi-constant throughout the weak inversion regime. It is of the order of 100 mV, similar to the saturation voltage of bipolar transistors.

- Drain currents in saturation are quasi-constant for the C.S.M. ignores effects like channel length modulation and DIBL. The transistor behaves like a perfect current source.

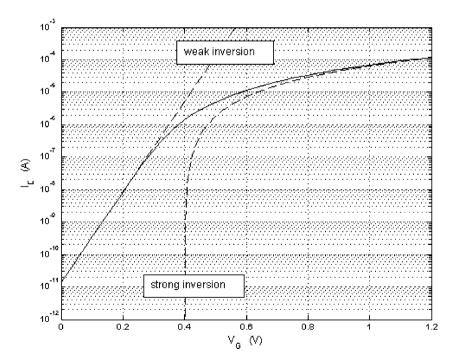

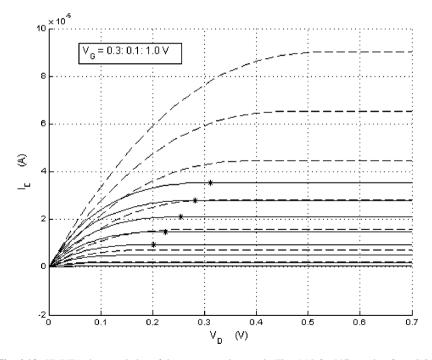

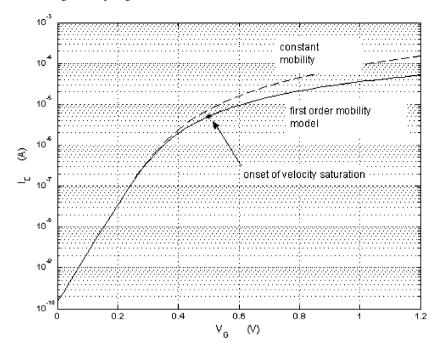

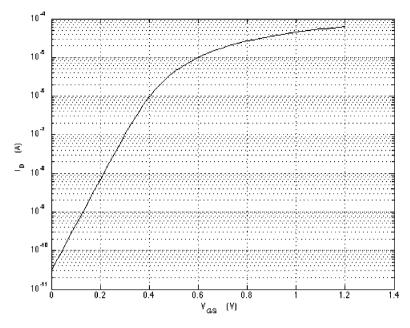

#### 2.4.2 The $I_D(V_G)$ Characteristic of the Saturated Transistor

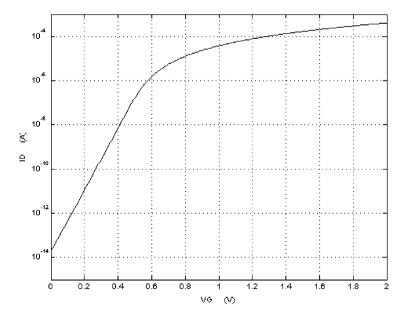

Figure 2.3 shows the drain current versus the gate voltage of the same transistor as above when saturated (the drain voltage  $V_D$  has no influence on the drain current). The almost linear section left attests clearly that below 0.5 V (weak inversion) the

Fig. 2.3 Drain current of the saturated common source transistor (MATLAB fig023.m)

drain current increases quasi-exponentially. In this region, the 'subthreshold' slope S determines the so-called slope factor n:

$$n = \frac{S}{U_T \log(10)} \tag{2.21}$$

Beyond the exponential, the drain current levels off gradually while the transistor is entering moderate and strong inversion. The trend in the strong inversion region is quadratic.

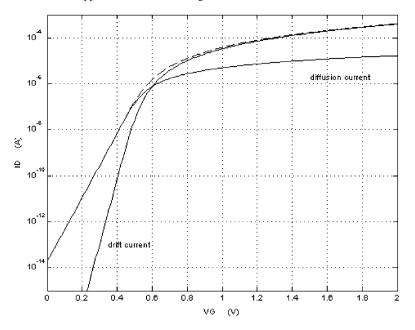

#### 2.4.3 Drift and Diffusion Contributions to the Drain Current

The C.S.M. offers the possibility to compare the contributions of drift and diffusion currents to the drain current. All what is needed therefore is to break the polynomial representation of  $I_D$  of Eq. 2.19 into two parts. For the diffusion current, the two last terms of Eq. 2.17 are considered and for the drift current what remains. The polynomials are respectively:

$$P_{diffusion} = \begin{bmatrix} 0 & 0 & U_T & \gamma U_T & 0 \end{bmatrix} \tag{2.22}$$

and

$$P_{drift} = \begin{bmatrix} -\frac{1}{2} - \frac{2}{3}\gamma & V_G & 0 & 0 \end{bmatrix}$$

(2.23)

The drift and diffusion currents displayed in Fig. 2.4 show clearly the dominance of one current over the other depending on which mode of operation is taking the lead. Diffusion dominates in weak inversion while drift takes over in strong inversion. In the middle, around 0.6 V, drift and diffusion currents have almost the same magnitudes. In strong inversion, the total current coincides practically with the quadratic approximation of  $I_D$ . The same holds true for the exponential current in weak inversion. Many analog circuits, especially low-power low-voltage circuits, operate nowadays in the so-called moderate inversion region.

#### 2.5 Weak Inversion Approximation of the Charge Sheet Model

The fact that diffusion current overwhelms drift current in weak inversion leads to a number of useful approximate expressions. Because the first of the two right terms of Eq. 2.6 can be ignored, one has:

$$I_D dx \approx -\mu C'_{ox} W U_T d\left(-\frac{Q'_i}{C'_i}\right)$$

(2.24)

Fig. 2.4 Same as Fig. 2.3 with explicit representations of the drift and diffusion currents (MATLAB fig024.m)

Consequently, the drain current in weak inversion is given by:

$$I_D \approx -\mu C'_{ox} \frac{W}{L} U_T \left[ \left( -\frac{Q'_{iD}}{C'_{ox}} \right) - \left( -\frac{Q'_{iS}}{C'_{ox}} \right) \right]$$

(2.25)

Let us find now an approximate expression of  $Q'_i/C'_{ox}$  in weak inversion. The inversion layer charge density is extracted from the equality:

$$-\frac{Q_i'}{C_{ox}'} = -\frac{Q_t'}{C_{ox}'} + \frac{Q_b'}{C_{ox}'}$$

(2.26)

where  $Q'_t/C'_{ox}$  and  $Q'_b/C'_{ox}$  are replaced by Eqs. 2.9 and 2.12. This leads to:

$$-\frac{Q_i'}{C_{ox}'} = \gamma \cdot \left[ U_T \exp\left(\frac{\psi_S - 2\phi_B - V}{U_T}\right) + \psi_S \right]^{1/2} - \gamma \sqrt{\psi_S}$$

(2.27)

Since the contribution of the first of the two terms under the square root (drift current) is small compared to that of the second (diffusion current), the equation above can be approximated as follows:

$$-\frac{Q_i'}{C_{ox}'} = \gamma \sqrt{small + \psi_S} - \gamma \sqrt{\psi_S} \approx \gamma \frac{small}{2\sqrt{\psi_S}}$$

(2.28)

This leads to:

$$-\frac{Q_i'}{C_{ox}'} \approx \gamma \frac{U_T}{2\sqrt{\psi_S}} \exp\left(\frac{\psi_S - 2\phi_B}{U_T}\right) \cdot \exp\left(-\frac{V}{U_T}\right)$$

(2.29)

The surface potential  $\psi_S$  depends practically only on the gate voltage. In weak inversion, Eq. 2.14 boils down indeed to a second order equation relating the gate voltage  $V_G$  to  $\psi_S$  for  ${Q'}_i/{C'}_{ox}$  is small in comparison to the contribution of the depletion layer represented by the two last terms. An expression of the weak inversion surface potential  $\psi_{Swi}$  can be extracted then from the latter:

$$\psi_{Swi} = \left[ -\frac{\gamma}{2} + \sqrt{\left(\frac{\gamma}{2}\right)^2 + V_G} \right]^2 \tag{2.30}$$

When  $\psi_{Swi}$  is put in Eq. 2.29 and the latter combined with Eq. 2.25, the next expression of the drain current in weak inversion is obtained:

$$I_{D} \approx \underbrace{\frac{1}{2}\beta\gamma U_{T}^{2} \frac{1}{\sqrt{\psi_{Swi}}} \exp\left(\frac{\psi_{Swi} - 2\phi_{B}}{U_{T}}\right)}_{A} \cdot \left[\exp\left(-\frac{V_{S}}{U_{T}}\right) - \exp\left(-\frac{V_{D}}{U_{T}}\right)\right]$$

(2.31)

This is an interesting result for it shows that the drain current in weak inversion is controlled exponentially by the source and drain voltages owing to the fact that the factor A depends only on the gate voltage. Another interesting observation concerns the drain voltage when the transistor enters saturation. Rewriting Eq. 2.31 in terms of the drain-to-source voltage difference  $V_{DS}$  turns the above expression into:

$$I_D \approx A \cdot \exp\left(-\frac{V_S}{U_T}\right) \cdot \left[1 - \exp\left(-\frac{V_{DS}}{U_T}\right)\right]$$

(2.32)

The drain current saturates as soon as the drain-to-source voltage attains  $100\,\text{mV}$  (nearly four times  $U_T$ ). The impact of the gate voltage is more difficult to apprehend for it is hidden in the A factor, which depends on the geometry via  $\beta$ , and  $\gamma$ ,  $\phi_B$  and the surface potential. The point is discussed more in detail further.

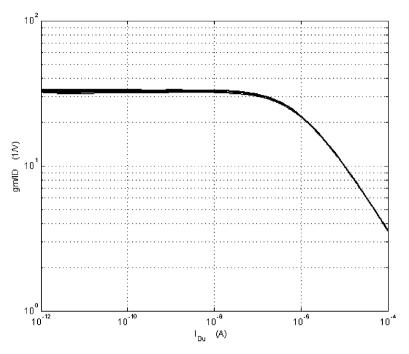

#### 2.6 The $g_m/I_D$ Ratio in the Common Source Configuration

An analytic expression of the transconductance over drain current ratio cannot be derived from the Charge Sheet Model. The ratio must be evaluated numerically by taking the derivative with respect to the gate voltage of the log of the drain current:

$$\frac{g_m}{I_D} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_G} = \frac{\partial \log (I_D)}{\partial V_G}$$

(2.33)

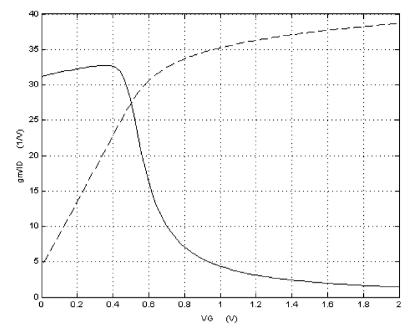

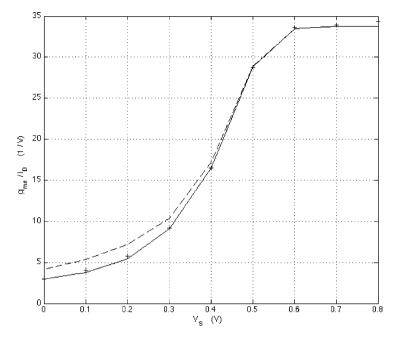

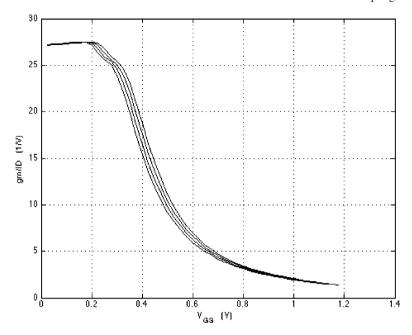

Fig. 2.5 The  $g_m/I_D$  ratio derived from the  $I_D(V_G)$  plot of Fig. 2.4, which is reproduced in the background (MATLAB fig025.m)

The  $g_m/I_D$  ratio is shown in Fig. 2.5. It is larger in weak than in strong inversion but displays a slightly decaying trend under very small currents. The phenomenon can be explained as follows. Consider the derivative versus the gate voltage of the expression hereafter extracted from Eq. 2.31:

$$\left(\frac{g_m}{I_D}\right)_{WI} \approx \frac{\partial}{\partial V_G} \log \left[\frac{1}{\sqrt{\psi_{Swi}}} \exp\left(\frac{\psi_{Swi} - 2\phi_B}{U_T}\right)\right]$$

(2.34)

The derivative is done into two steps, first with respect to  $V_G$ , second to  $\psi_{Swi}$ :

$$\left(\frac{g_m}{I_D}\right)_{W.I.} \approx \left(-\frac{1}{2\psi_{Swi}} + \frac{1}{U_T}\right) \frac{\partial \psi_{Swi}}{\partial V_G}$$

(2.35)

When the derivative of the weak inversion surface potential with respect to the gate voltage is extracted from Eq. 2.30, one has:

$$\left(\frac{g_m}{I_D}\right)_{W.I.} = \frac{1}{UT} \cdot \frac{1 - \frac{U_T}{2\psi_{Swi}}}{1 + \frac{\gamma}{2\sqrt{\psi_{Swi}}}}$$

(2.36)

Notice the similarity with the approximate  $g_m/I_D$  ratio of Eq. 1.13 in the first chapter, stating that:

$$\left(\frac{g_m}{I_D}\right)_{W.I.} = \frac{1}{n U_T} \tag{2.37}$$

The comparison of Eq. 2.36 with 2.37 brings about an interesting analytical expression of the weak inversion subthreshold slope factor, called  $n_{wi}$ :

$$n_{wi} = \frac{1 + \frac{\gamma}{2\sqrt{\psi_{Swi}}}}{1 - \frac{U_T}{2\psi_{Swi}}} \tag{2.38}$$

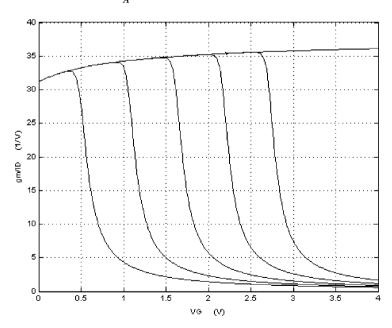

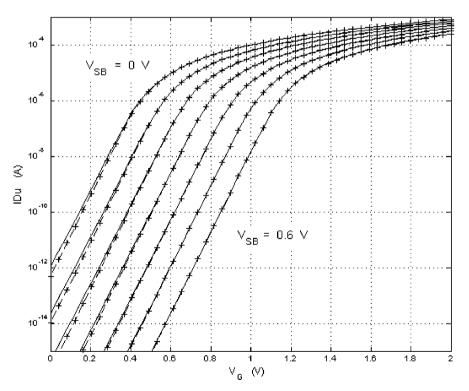

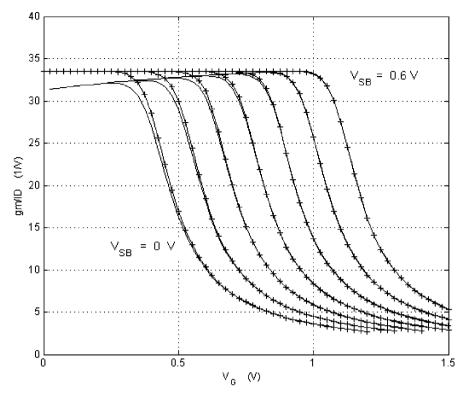

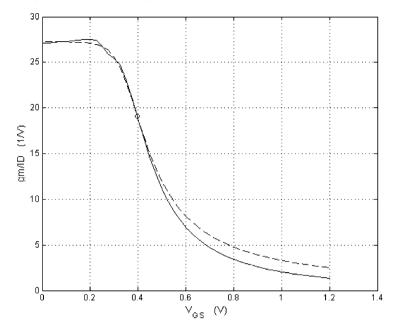

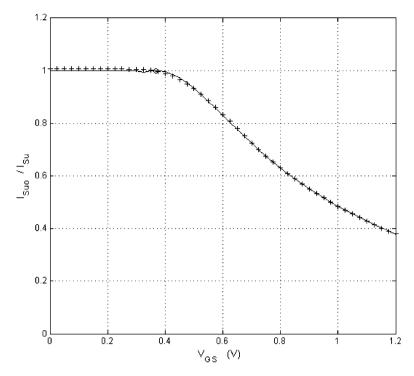

The signification of  $n_{wi}$  gets clear when several  $g_m/I_D$  plots are merged as their source voltages changes. Figure 2.6 shows clearly that when the transistor enters weak inversion, all  $g_m/I_D$  ratios come together forming a single consolidated envelope, which coincides with Eq. 2.36.

Near the origin, the envelope bends down more rapidly for the width of the depleted region under the gate is getting smaller as the source voltage decreases. The ratio of the capacitive divider formed by the gate oxide and the depleted region increases, modifying consequently the slope factor  $n_{wi}$ .

One may substitute a more compact and more familiar expression to Eq. 2.31:

$$I_D \approx \underbrace{I_o \exp\left(\frac{V_G}{n_{wi}U_T}\right)}_{4} \cdot \left[\exp\left(-\frac{V_S}{U_T}\right) - \exp\left(-\frac{V_D}{U_T}\right)\right]$$

(2.39)

Fig. 2.6 Plot of  $g_m/I_D$  ratios when the source voltage changes from 0 V (*left*) to 2 V (*right*) in steps 0.5 V wide. The distance separating  $g_m/I_D$ 's is a little more than 0.5 V owing to the body-effect discussed more in detail in the next chapter (MATLAB fig026.m)

#### 2.7 Common Gate Characteristics of the Saturated Transistor

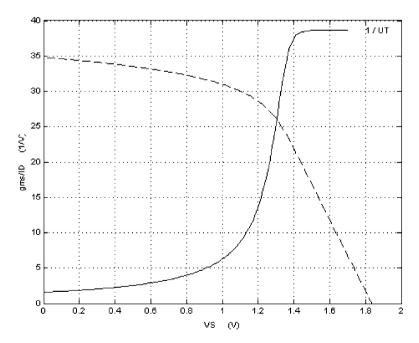

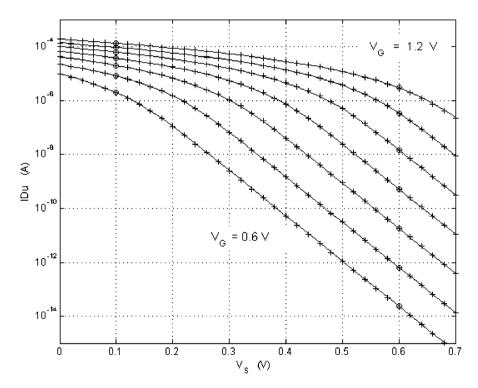

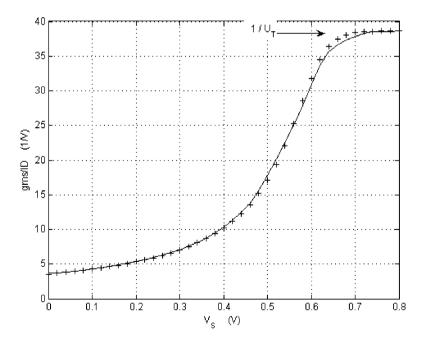

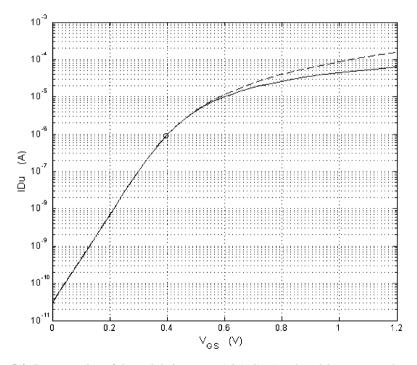

Let us consider now the common-gate configuration. The gate voltage is fixed while the source  $V_S$  is the input now. Figure 2.7 shows the  $I_D(V_S)$  curve obtained after running the same file as above when the gate voltage is equal to 2 V and the source voltage  $V_S$  varies from 0 to 2 V. The drain voltage is supposed to be large enough in order to keep the transistor saturated under any circumstance. As  $V_S$  increases, the gate-to-source voltage  $V_{GS}$  decreases abating the drain current. First, the drain current slows down gradually for the transistor is still in strong inversion. Once the transistor is in weak inversion, the current decreases exponentially. In this region, the slope of the drain current follows the  $\exp(V_S/U_T)$  law predicted by Eq. 2.31. Put differently, the slope factor is equal to one in strong contrast with the slope factor of the common source slope factor.

The same plot shows also the  $g_{ms}/I_D$  ratio inferred from the drain current characteristic. Like in the common-source configuration, the ratio is given by the slope of the semilog-scaled drain current. The 'transconductance' is now  $g_{ms}$  instead of  $g_m$ . The sequence is being reversed with respect to the common-source configuration for the  $g_{ms}/I_D$  is flipped horizontally with respect to  $g_m/I_D$ .

In weak inversion, the  $g_{ms}/I_D$  ratio is equal to  $I/U_T$  in accordance with the unity slope factor mentioned above. This once again underlines the similarity MOS

Fig. 2.7 The  $g_{ms}/I_D$  ratio (plain lines) versus the source voltage is obtained by taking the derivative of the log scaled drain current plotted in dashed lines ( $V_G$  is equal to 2 V) (MATLAB fig027.m)

transistors share with bipolar transistors when operating in weak inversion. Two reasons explain this. First, the drain current is dominated by diffusion current as in the neutral base of the bipolar transistor. Second, the front and back gates cooperate whereas the back-gate remains idle in the common source configuration. The common-gate configuration ignores consequently the partitioning inherent to the common-source configuration.

We will show in later chapters that real transistors do not conform to the unity slope factor in weak inversion in the common-gate configuration. The slope factor is generally slightly larger than one. This is due to the drain-to-source voltage variation going along with the gate-to-source voltage modifications. In the C.S.M. the drain voltage has no effect on the current as long as the transistor is saturated, but with real transistors, changes of the drain voltage modify the space charge near the drain and below the inversion layer. The drain influences thus the current even though the transistor is saturated. The  $g_{ms}/I_D$  ratio of real transistors in weak inversion is smaller thus than the predicted  $1/U_T$ .

#### 2.8 A Few Concluding Remarks Concerning the C.S.M.

The Charge Sheet Model is a physical model that predicts drain currents whatsoever mode of operation, weak or strong inversion, saturation or not. It is relevant and particularly instrumental for understanding the basic mechanisms controlling low-power operation. In addition, the model bridges drain currents to physical quantities such as the substrate impurity concentration, oxide thickness and temperature. It offers therefore the possibility to scrutinize sensitivity aspects. The validity of the C.S.M. is restricted however to ideal transistors implemented in a uniformly doped substrate with gate lengths sufficiently large to obliterate short channel effects.

An interesting observation can be made as far as the *threshold voltage*. So far, the concept has not been mentioned except occasionally, for instance when the quadratic model was considered. The Charge Sheet Model ignores actually the concept. The reason is that the threshold voltage is not a physical quantity but a parameter embodied on measurements. Its interpretation varies according to the evaluation techniques. This does not mean that the threshold voltage is a useless concept. On the contrary, it is a landmark, like the voltage drop across forward biased junctions. It is an essential parameter exploited in every circuit oriented model. In the next chapter, we are going to clarify the concept.

## Chapter 3

# **Graphical Interpretation of the Charge Sheet Model**

#### 3.1 A Graphical Representation of $I_D$

An interesting representation of the drain current can be obtained when the expression below is used for the drain current (Tsividis 1999):

$$I_D = \mu C'_{ox} \frac{W}{L} \cdot \int_{V_S}^{V_D} \left( -\frac{Q'_i}{C'_{ox}} \right) dV$$

(3.1)

The equation is derived from, the proportionality of the minority carrier density to the exponential function acknowledged by Boltzmann statistics:

$$Q_i' \propto \exp\left(\frac{\psi_S - 2\phi_B - V}{U_T}\right)$$

(3.2)

After differentiating the two sides of the above expression, an equation connecting the differentials of  $Q'_i$ ,  $\psi_S$  and V is obtained:

$$U_T \frac{dQ_i'}{Q_i'} = d\psi_S - dV \tag{3.3}$$

This enables us to replace the drift and diffusion current contributions considered in the previous chapter by a single term,  $Q'_i d\psi_S$ , turning Eq. 2.7 into the expression below, which leads to Eq. 3.1 after integration:

$$I_D dx = \mu C'_{ox} W \left( -\frac{Q'_i}{C'_{ox}} \right) dV$$

(3.4)

Although Eq. 3.1 is more compact than Eq. 2.8, we haven't booked any progress for the integration has to be carried out now with respect to the channel voltage V while the expression between brackets is a function of the surface potential  $\psi_S$  as reminded by Eq. 2.15 reproduced hereunder for convenience:

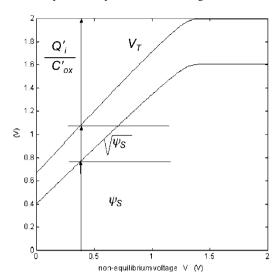

Fig. 3.1 Representation versus the non-equilibrium voltage V of the surface potential  $\psi_S$  and the threshold voltage with respect to the substrate  $V_T$ . The p vector is given by pMat(300,1e17,5) and the gate voltage equal to 2 V (MATLAB fig031.m)

$$-\frac{Q_i'}{C_{ox}'} = V_G - \gamma \sqrt{\psi_S} - \psi_S \tag{3.5}$$

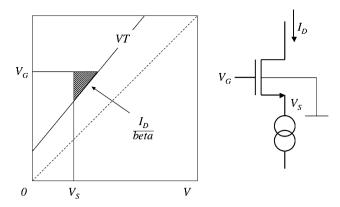

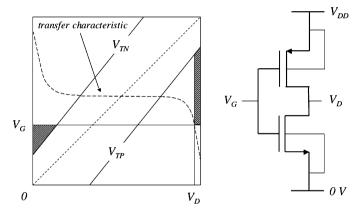

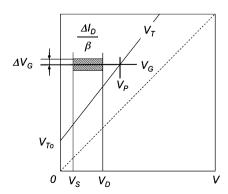

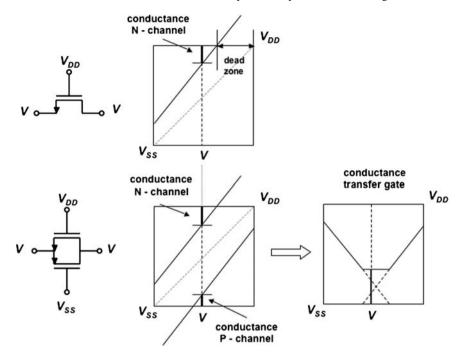

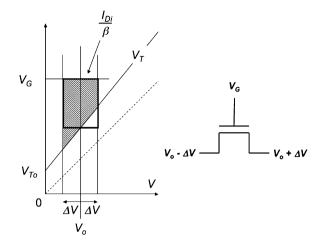

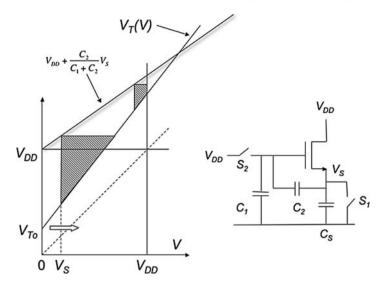

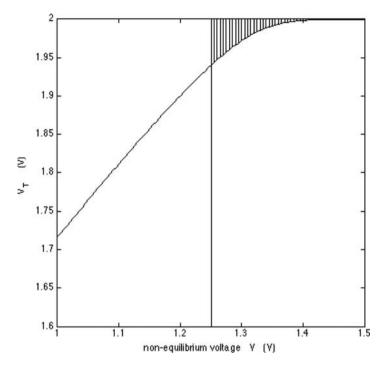

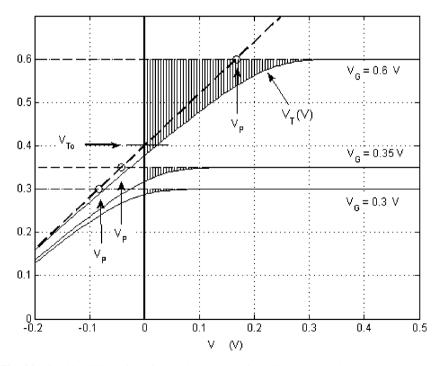

Equations 3.4 and 3.5 pave the road however towards a graphical interpretation of the drain current. The idea is illustrated by the two curves shown in Fig. 3.1: the lower one representing the surface potential  $\psi_S$  versus the non-equilibrium voltage V, the upper one, called  $V_T$ , the sum hereunder:

$$V_T = \gamma \sqrt{\psi_S} + \psi_S \tag{3.6}$$

According to Eqs. 3.5 and 3.6,  $V_T$  is the voltage to apply to the gate in order to zero the mobile charge density  $Q'_i$ . When  $V_G$  is larger than  $V_T$ , the semiconductor surface is inverted and when  $V_G$  is smaller than  $V_T$  there is no inversion layer. Hence,  $V_T$  can be assimilated to a kind of *threshold voltage*, which should not be confused with the threshold voltage  $V_{th}$  currently associated to the quadratic representation of the drain current. The first is defined with respect to the substrate, the second with respect to the source.

Because the difference between  $V_G$  and the threshold voltage  $V_T$  is in a representation of  $-Q'_i/C'_{ox}$ , we may rewrite Eq. 3.1 as follows:

$$I_D = \mu C'_{ox} \frac{W}{L} \cdot \int_{V_S}^{V_D} (V_G - V_T) \ dV$$

(3.7)

Fig. 3.2 Graphical illustration of the drain current of a MOS transistor whose  $V_S$  and  $V_D$  are respectively equal to 0.3 and 1.0 V. The gate voltage, oxide thickness, substrate doping and temperature are the same as in Fig. 3.1 (MATLAB fig032.m)

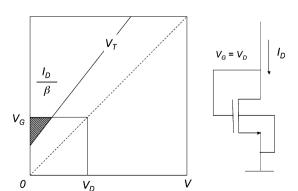

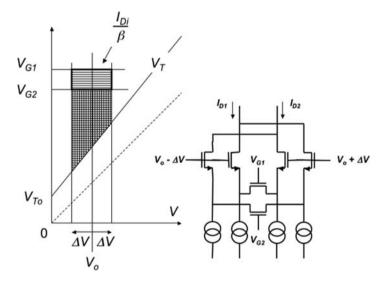

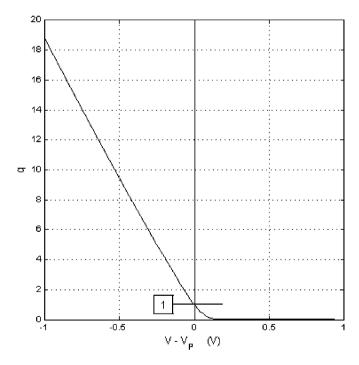

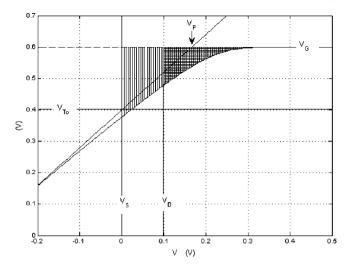

This leads to the graphical interpretation of the drain current<sup>1</sup> represented by the hatched area of Fig. 3.2. The surface delineated by  $V_G$  and  $V_T$  and the vertical lines  $V_S$  and V is indeed a representation of the drain current divided by  $\beta$  according to Eq. 3.7. This representation can be used in order to visualize how the terminal voltages control the drain current. Consider for instance a grounded source transistor whose drain voltage  $V_D$  increases gradually, starting from zero. When  $V_D$  is small, the area representing the drain current divided by beta resolves to a narrow stripe very close to the vertical axis like in the first of the four views shown in Fig. 3.3. As the drain voltage increases, the area widens but the growth rate declines as we approach the point where  $V_T$  gets close to  $V_G$ . Beyond this point, the drain current does not increase anymore for the triangularly shaped area representing the drain current remains practically constant. We reached the *pinch-off voltage*. The transistor is now saturated.

<sup>&</sup>lt;sup>1</sup> The graphical interpretation of the drain current is designated generally by the name their authors Memelink–Jespers. It was reported first in (Jespers et al. 1977) and taken over in a number of publications among which Cand et al. (1986), Wallinga and Bult (1989) and Enz and Vittoz (2006).

Fig. 3.3 Graphical illustration of  $I_D(V_D)/beta$  considering a grounded source transistor with a constant  $V_G$  of 2 V and a drain voltages stepping from 0.050 V, to 0.250 V, 0.750 V and 2,00 V (MATLAB fig033.m)

# 3.2 More on the $V_T$ Curve

Before we illustrate by means of a few examples the use that can be made of the graphical construction, we look more closely to the surface potential curve shown in Fig. 3.1 in order to explain its shape.

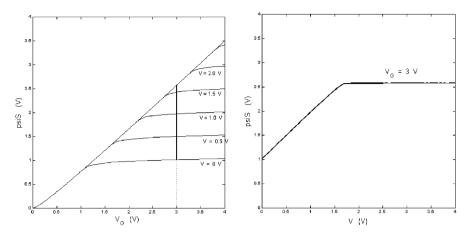

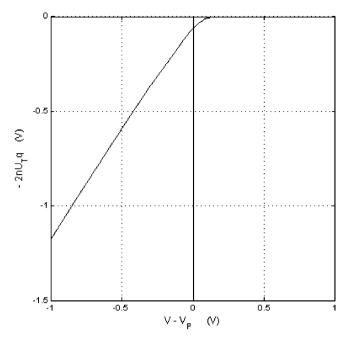

Figure 3.4 shows two representations of  $\psi_S$ . The left one traces the surface potential  $\psi_S$  versus the gate voltage  $V_G$  considering a series of constant non-equilibrium voltages V increments from 0 to 2 V in steps of 0.5 V. The right figure shows similar data, plotted versus the non-equilibrium voltage V.