**ACSP** · Analog Circuits and Signal Processing

Elie Maricau Georges Gielen

# Analog IC Reliability in Nanometer CMOS

#### Analog Circuits and Signal Processing

Series Editors

Mohammed Ismail, The Ohio State University Mohamad Sawan, École Polytechnique de Montréal

For further volumes: http://www.springer.com/series/7381

# Analog IC Reliability in Nanometer CMOS

Elie Maricau ESAT-MICAS KU Leuven Heverlee Belgium Georges Gielen ESAT-MICAS KU Leuven Heverlee Belgium

ISBN 978-1-4614-6162-3 ISBN 978-1-4614-6163-0 (eBook) DOI 10.1007/978-1-4614-6163-0 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2012954854

#### © Springer Science+Business Media New York 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Abstract**

Today, micro-electronic circuits are undeniably and ubiquitously present in our society. Transportation vehicles such as cars, trains, buses, and airplanes make abundant use of electronic circuits to reduce energy consumption and emission of greenhouse gases and to increase passenger safety and travel comfort. Other products using electronic circuits are smartphones, tablet PCs, game consoles, household appliances, satellites, base stations, servers, etc. Each of these applications is becoming increasingly more complex to build. At the same time, the quality and reliability requirements for electronic circuits are more demanding than ever.

To guarantee a high production yield and a sufficient circuit lifetime, possible hazards and failure effects have to be considered throughout the entire design flow. Such a flow includes the initial concept, the design itself, the testing of the prototype circuit, and finally the production process. The majority of integrated circuits manufactured today is processed in a complementary metal-oxide semiconductor (CMOS) technology. To reduce cost and to increase performance, the dimensions of all circuit components are shrinked with each new technology node. Associated with this technology scaling are the atomistic size of modern transistors, an increase of the gate-oxide electric field, and the introduction of new gate and channel materials. The combination of these elements results in an emerging reliability problem for advanced nanometer CMOS technologies. Transistor wearout manifests itself as a gradual and time-dependent shift of circuit characteristics which can result in circuit failure. Especially analog circuits, which are typically used as an interface between the real world and a digital backend, can be very sensitive to such small circuit parameter variations.

This work focuses on the simulation and analysis of analog circuit reliability. The models and simulation techniques proposed in this dissertation are aimed to serve as an aid for circuit designers to better understand the impact of aging effects on their circuits and to enable the development of failure-resilient design solutions.

In a first part of the work, an overview of all relevant nanometer CMOS unreliability effects is given and transistor compact models for the most important

vi Abstract

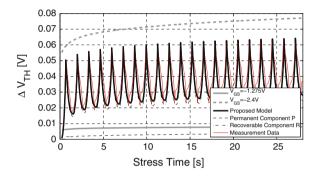

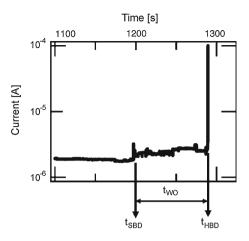

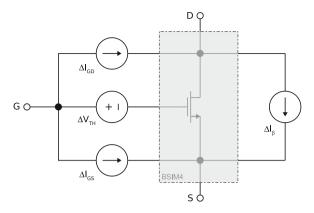

aging effects are proposed. A distinction between spatial unreliability effects, resulting from process variations, and temperoral unreliability effects, which are time-dependent, can be made. The latter can again be divided into transient effects such as noise and electromagnetic interference, and aging effects such as breakdown, bias temperature instability, and hot carrier injection. This work primarily concentrates on the aging effects. To enable efficient and accurate circuit lifetime simulations, transistor compact models for each aging effect are proposed. These models include the most important circuit-related stress parameters such as voltages, transistor dimensions, and temperature. Important effects such as partial recovery of the transistor damage when the stress voltage is reduced, are also supported. Each model is validated with measurements. Also, models for stochastic aging effects in sub-45 nm CMOS, which result in time-dependent transistor mismatch, are discussed.

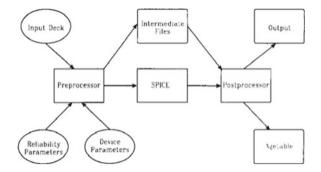

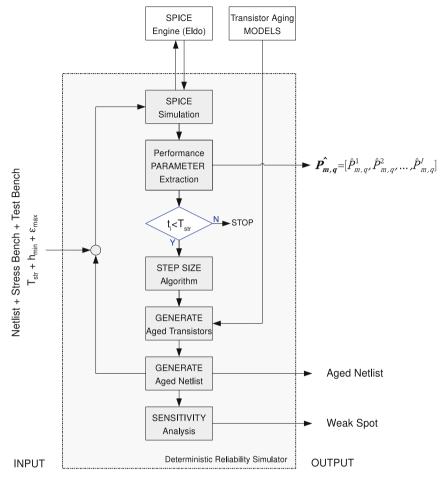

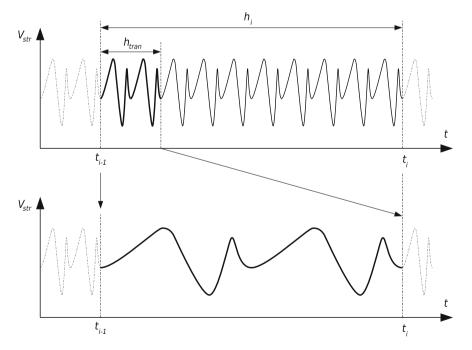

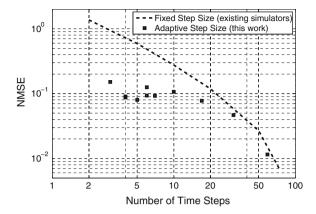

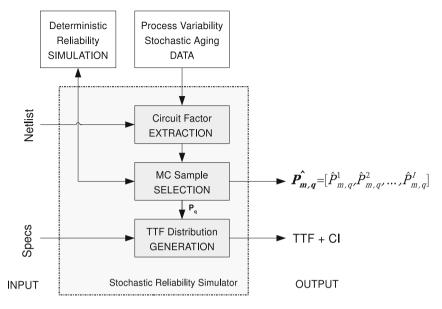

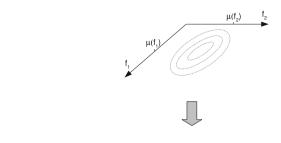

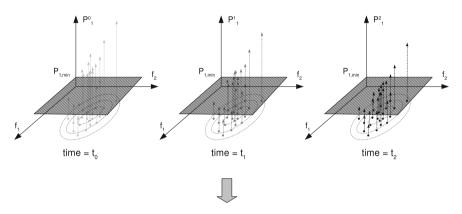

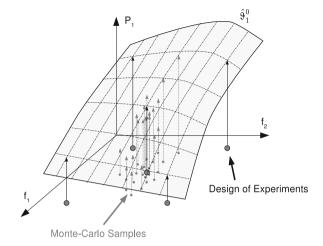

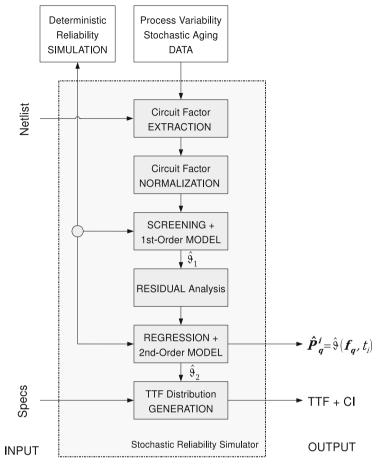

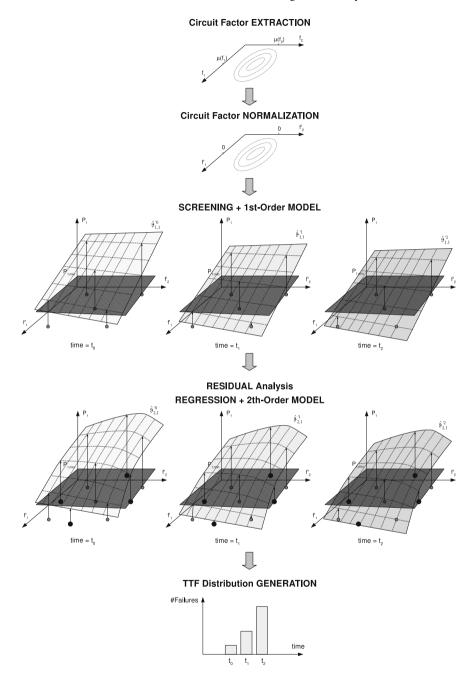

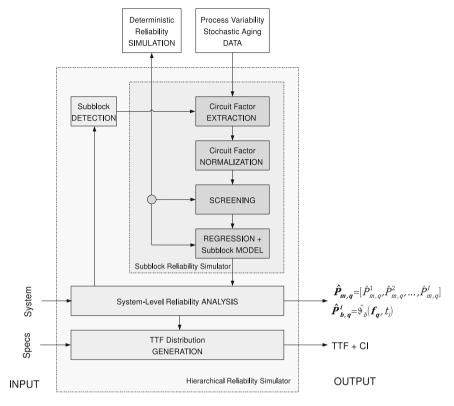

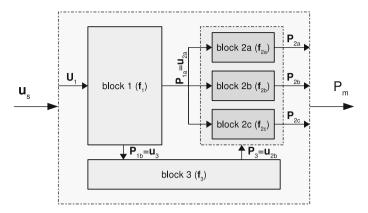

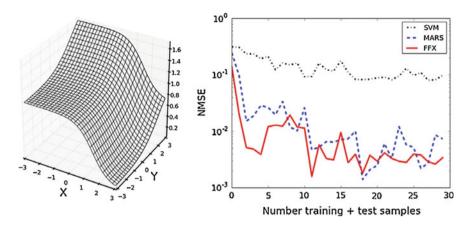

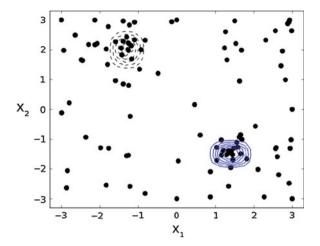

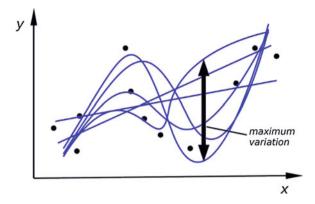

A second part of the book focuses on the development of efficient simulation methods to analyze the impact of transistor aging on an entire circuit. Existing reliability simulators, published in the literature or commercially available, still suffer from a lot of deficiencies. Often, these tools do not support all unreliability effects and especially the impact of process variations and stochastic aging effects is in most cases not included. The tool set presented in this work aims to solve these problems, while still limiting the computational effort. The proposed simulator includes support for all important deterministic and stochastic aging effects. Further, the interaction between process variations and aging effects can be analyzed and visualized. In addition to a visualization of the time-dependent performance shift of the circuit under test, reliability weak spots can be detected. This enables a designer to search for dedicated solutions in case of a reliability problem. To limit the simulation time, the simulator uses a response surface method which models the time-dependent circuit performance based on only a limited set of SPICE-based reliability simulations. Finally, a hierarchical simulation framework based on an adaptive sample selection algorithm and a nonlinear symbolic regression algorithm enables the reliability simulation of large analog circuits within a reasonable time frame. Each part of the simulation framework is demonstrated on an example circuit.

The last part of this work applies the proposed reliability compact models and simulation methods to a set of commonly used analog circuits. Factors that determine the circuit lifetime are explored and illustrated with examples. Further, a design for reliability flow is demonstrated on an example IDAC circuit resulting in the design of a reliable circuit with minimum guardbanding. Finally, the lifetime of small- to medium-sized digital circuits is investigated. Although, the methods proposed in this work are primarily intended for analog circuits, they are also applicable to small- and medium-sized digital circuits when these are defined as a SPICE netlist.

The models and simulation techniques developed in this work are intended as a first step towards understanding the impact of transistor aging on analog integrated circuits. Eventually, this understanding can help designers in designing guaranteed reliable and robust circuits in future CMOS process nodes.

#### **Contents**

| 1 | Intr | oduction                                         |  |  |  |  |  |

|---|------|--------------------------------------------------|--|--|--|--|--|

|   | 1.1  | Introduction                                     |  |  |  |  |  |

|   | 1.2  | Reliability Engineering: A Brief History         |  |  |  |  |  |

|   | 1.3  | Reliability of Electronic Systems                |  |  |  |  |  |

|   | 1.4  | Reliability in Nanometer CMOS                    |  |  |  |  |  |

|   |      | 1.4.1 Reduction of the Effective Oxide Thickness |  |  |  |  |  |

|   |      | 1.4.2 Introduction of New Materials and Devices  |  |  |  |  |  |

|   |      | 1.4.3 Atomic-Scale Dimensions                    |  |  |  |  |  |

|   |      | 1.4.4 Mission Profiles                           |  |  |  |  |  |

|   |      | 1.4.5 Time and Money Constraints                 |  |  |  |  |  |

|   | 1.5  | Design for Reliability                           |  |  |  |  |  |

|   |      | 1.5.1 Define                                     |  |  |  |  |  |

|   |      | 1.5.2 Identify                                   |  |  |  |  |  |

|   |      | 1.5.3 Analyze and Assess                         |  |  |  |  |  |

|   |      | 1.5.4 Quantify, Improve and Validate             |  |  |  |  |  |

|   |      | 1.5.5 Monitor and Control                        |  |  |  |  |  |

|   | 1.6  | Conclusions                                      |  |  |  |  |  |

| 2 | CM   | OS Reliability Overview                          |  |  |  |  |  |

|   | 2.1  | Introduction                                     |  |  |  |  |  |

|   | 2.2  |                                                  |  |  |  |  |  |

|   | 2.3  | Spatial Unreliability                            |  |  |  |  |  |

|   |      | 2.3.1 Systematic Effects                         |  |  |  |  |  |

|   |      | 2.3.2 Random Effects                             |  |  |  |  |  |

|   | 2.4  | Temporal Unreliability                           |  |  |  |  |  |

|   |      | 2.4.1 Aging Effects                              |  |  |  |  |  |

|   |      | 2.4.2 Transient Effects                          |  |  |  |  |  |

|   | 2.5  | Conclusions                                      |  |  |  |  |  |

viii Contents

| 3 | Tra | nsistor Aging Compact Modeling                            | 7 |

|---|-----|-----------------------------------------------------------|---|

|   | 3.1 | Introduction                                              | 7 |

|   | 3.2 | Hot Carrier Injection                                     | 8 |

|   |     | 3.2.1 Background                                          | 8 |

|   |     | 3.2.2 A HCI Compact Model for Circuit Simulation 4        | 0 |

|   |     | 3.2.3 HCI in Sub-45 nm CMOS                               | 6 |

|   | 3.3 | Bias Temperature Instability                              | 7 |

|   |     | 3.3.1 Background                                          | 7 |

|   |     | 3.3.2 A BTI Compact Model for Circuit Simulation 5        | 5 |

|   |     | 3.3.3 Model Calibration and Validation 6                  | 1 |

|   |     | 3.3.4 BTI in Sub-45 nm CMOS 6                             | 8 |

|   | 3.4 | Time-Dependent Dielectric Breakdown 6                     | 9 |

|   |     | 3.4.1 Hard Breakdown                                      | 0 |

|   |     | 3.4.2 Soft Breakdown                                      | 1 |

|   | 3.5 | Aging-Equivalent Transistor Model                         | 3 |

|   |     | 3.5.1 Threshold Voltage 7                                 | 3 |

|   |     | 3.5.2 Carrier Mobility                                    | 4 |

|   |     | 3.5.3 Oxide Breakdown                                     | 5 |

|   | 3.6 | Aging Model for Hand Calculations                         | 5 |

|   | 3.7 | Conclusions                                               | 6 |

|   |     |                                                           |   |

| 4 | Bac | kground on IC Reliability Simulation                      | 9 |

|   | 4.1 | Introduction                                              |   |

|   | 4.2 | Literature Overview                                       | 0 |

|   |     | 4.2.1 Berkeley Reliability Tools (BERT) 8                 | 0 |

|   |     | 4.2.2 Other Reliability Simulators 8                      | 3 |

|   | 4.3 | Commercial Reliability Simulators 8                       |   |

|   |     | 4.3.1 The Mentor Graphics Reliability Simulator 8         | 4 |

|   |     | 4.3.2 The Cadence Reliability Simulator (BERT/RelXpert) 8 | 6 |

|   |     | 4.3.3 The Synopsys Reliability Simulator (MOSRA) 8        |   |

|   | 4.4 | Discussion                                                | 9 |

|   | 4.5 | Conclusions                                               | 1 |

| 5 | Δna | log IC Reliability Simulation                             | 3 |

|   | 5.1 | Introduction                                              |   |

|   | 5.2 | Deterministic Reliability Simulation                      |   |

|   | 5.2 | 5.2.1 Problem Statement                                   | - |

|   |     | 5.2.2 Implementation                                      |   |

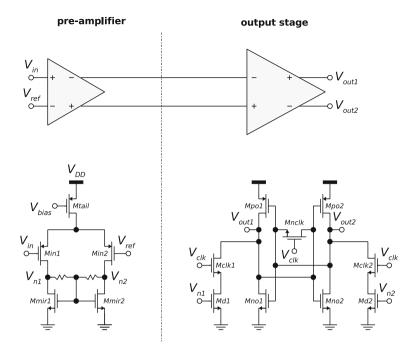

|   |     | 5.2.3 Circuit Example                                     |   |

|   | 5.3 | Stochastic Reliability Simulation                         |   |

|   | 5.5 | 5.3.1 Problem Statement                                   |   |

|   |     | 5.3.2 Implementation 1: Monte-Carlo Simulation            |   |

|   |     | 5.3.3 Implementation 2: A Response Surface Methodology 11 |   |

|   |     | 2.2.2 Implementation 2. 11 response pullace Membratical 2 |   |

Contents ix

|     |                                    | 5.3.4   | Circuit Example                                     | 131 |  |  |  |

|-----|------------------------------------|---------|-----------------------------------------------------|-----|--|--|--|

|     | 5.4                                |         | rchical Reliability Simulation                      | 136 |  |  |  |

|     |                                    | 5.4.1   | Problem Statement                                   | 136 |  |  |  |

|     |                                    | 5.4.2   | Implementation                                      | 137 |  |  |  |

|     |                                    | 5.4.3   | Circuit Example                                     | 146 |  |  |  |

|     | 5.5                                | Concl   | usions                                              | 149 |  |  |  |

| 6   | Inte                               | grated  | Circuit Reliability                                 | 151 |  |  |  |

|     | 6.1                                | Introd  | uction                                              | 151 |  |  |  |

|     | 6.2                                | Assess  | sment                                               | 152 |  |  |  |

|     |                                    | 6.2.1   | Observed Performance Parameter                      | 153 |  |  |  |

|     |                                    | 6.2.2   | Process Capability Index                            | 155 |  |  |  |

|     |                                    | 6.2.3   | Technology                                          | 158 |  |  |  |

|     |                                    | 6.2.4   | Circuit Design                                      | 159 |  |  |  |

|     |                                    | 6.2.5   | Stress Conditions                                   | 160 |  |  |  |

|     | 6.3                                | Failur  | e-Resilient Circuits                                | 160 |  |  |  |

|     |                                    | 6.3.1   | Intrinsically Robust Circuits                       | 161 |  |  |  |

|     |                                    | 6.3.2   | Self-healing Circuits                               | 163 |  |  |  |

|     | 6.4                                | Case S  | Study 1: IDAC                                       | 164 |  |  |  |

|     |                                    | 6.4.1   | Technology                                          | 166 |  |  |  |

|     |                                    | 6.4.2   | Conventional Design                                 | 167 |  |  |  |

|     |                                    | 6.4.3   | Reliability-Aware Design: Fixed Topology            | 168 |  |  |  |

|     |                                    | 6.4.4   | Reliability-Aware Design: Digitally-Assisted Analog | 170 |  |  |  |

|     | 6.5 Case Study 2: Digital Circuits |         |                                                     |     |  |  |  |

|     |                                    | 6.5.1   | Digital Circuit Lifetime                            | 172 |  |  |  |

|     |                                    | 6.5.2   | Minimum Circuit Lifetime                            | 173 |  |  |  |

|     |                                    | 6.5.3   | Example Circuit                                     | 175 |  |  |  |

|     | 6.6                                | Concl   | usions                                              | 179 |  |  |  |

| 7   | Con                                | alucian | s                                                   | 181 |  |  |  |

| ′   | 7.1                                |         | al Conclusions                                      | 181 |  |  |  |

|     | /.1                                | Gener   | at Conclusions                                      | 101 |  |  |  |

| Bil | bliogr                             | aphy .  |                                                     | 185 |  |  |  |

| Inc | dex .                              |         |                                                     | 195 |  |  |  |

#### **Abbreviations**

AC Alternating Current

ADC Analog-to-Digital Converter AEC Automotive Electronics Council

ALT Accelerated Life Test

AMS Analog and Mixed Signal

BERT Berkeley Reliability Tools

BSIM Berkeley Short-channel IGFET Model

BTI Bias Temperature Instability

CDF Cumulative Density Function

CMOS Complementary Metal-Oxide-Semiconductor

CHE Channel Hot Electron

CP Charge Pumping

DAC Digital-to-Analog Converter DAHC Drain Avalange Hot Carrier

DC Direct Current

DFR Design For Reliability

DPT Design Patterning Technology

DUT Device Under Test

eMSM extended Measurement Stress Measurement

EM ElectroMigration

EMI ElectroMagnetic Interference

ENOB Effective Number Of Bits

EOT Effective Oxide Thickness

EUVL Extreme Ultraviolet Lithography

ESD ElectroStatic Discharge

FET Field Effect Transistor

FF Fractional Factorial

FFX Fast Function eXtraction

FMEA Failure Mode Effect Analysis

FTC Fast Transient Charging

GBW Gain-BandWidth

xii Abbreviations

HALT Highly Accelerated Life Test HASS Highly Accelerated Stress Test

HBD Hard Breakdown

HCI Hot Carrier Injection

HKMG High-K Metal Gate

IC Integrated Circuit

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

IL Interfacial Layer

ITRS International Technology Roadmap for Semiconductors

LEM Lucky Electron Model

LER Line Edge Roughness

LHS Latin Hypercube Sampling

LWR Line Width Roughness

MARS Multivariate Adaptive Regression Splines

MC Monte Carlo

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MT Multiple Trapping

MTTF Mean Time To Failure

NBTI Negative Bias Temperature Instability

NF Noise Figure

nMOS n-type MOS Transistor

NMSE Normalized Mean Square Error OPC Optical Proximity Correction

OTF On The Fly

PBD Progressive Breakdown

PBTI Positive Bias Temperature Instability

PCB Printed Circuit Board

PDF Probability Density Function pMOS p-type MOS Transistor PVT Process Voltage Temperature

RD Reaction Diffusion

RDD Reaction Dispersive Diffusion RDF Random Dopand Fluctuation

RF Radio Frequent

RMS Root Mean Square

RTL Register Transfer Level

RTN Random Telegraph Noise

SBD Soft Breakdown SEU Single Event Upset

SGHE Secondary Generated Hot Electron

SHE Substrate Hot Electron SNR Signal-to-Noise Ratio

SPICE Simulation Program with Integrated Circuit Emphasis

SR Symbolic Regression

Abbreviations xiii

SSN Simultaneous Switching Noise

SSPA Switching Sequence Post Adjustment

SVM Support Vector Machines

TDDB Time Dependent Dielectric Breakdown

TFR Test For Reliability

TTF Time To Failure

UDRM User Defined Reliability Model VCO Voltage Controlled Oscillator

#### **Symbols and Quantities**

$A_{

m VTH}$

```

Oxide capacitance

C_{\rm ox}

Activation energy

E_{a}

Lateral electric field

E_{\rm lat}

E_{ox}

Oxide electric field

Small signal output conductance

g_0

Drain-source current

I_{\rm DS}

I_{GS}

Gate-source current

Substrate current

I_{\rm sub}

Boltzmann constant (1.3806503 \times 10^{23} \text{ J/K})

k

BTI forward dissociation rate

k_{\rm F}

BTI annealing rate

k_{\rm R}

L

Transistor length

N_{\rm IT}

Number of interface traps

Number of oxide traps

N_{\rm OT}

Electron charge (1.602 \times 10^{-19} \text{ C})

(Mean) time to breakdown

t_{\rm RD}

Oxide thickness

t_{\rm ox}

Temperature

T_{\rm str}

Total stress time

Bulk-source voltage

V_{\rm BS}

V_{\rm DS}

Drain-source voltage

Gate-source voltage

V_{\rm GS}

V_{

m str}

Stress voltage

Threshold voltage

V_{\mathrm{TH}}

W

Transistor with

β

Carrier mobility

(Aging induced) parameter shift

Δ

(Process induced) parameter variation

δ

Oxide permittivity

\varepsilon_{ox}

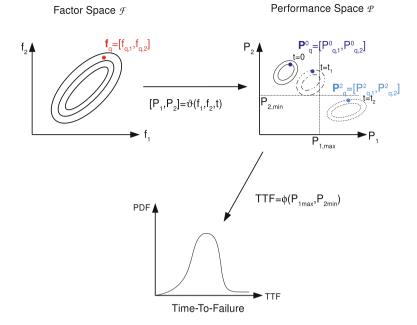

Factor space

```

Mismatch technology parameter

$\phi_{\mathrm{IT.e}}$  Critical energy for electrons to create an interface trap

$\lambda_e$  Hot-electron mean free path

$\mu$  Mean

$\mathcal{P}$  Performance space  $\sigma$  Standard deviation

$\vartheta$  Relation between factor space and performance space

### Chapter 1 Introduction

#### 1.1 Introduction

This work aims to provide the reader with a comprehensive understanding on the subject of modeling, analyzing and understanding the impact of transistor aging on analog integrated circuits (IC) in a nanometer complementary metal-oxide-semiconductor (CMOS) technology. The first chapter of this work introduces the problem studied and the major subjects addressed in this book.

The chapter is outlined as follows. First, a brief history of reliability engineering is given in Sect. 1.2. Then, Sect. 1.3 discusses the importance of reliability in electronic systems today. Depending on the application, different circuit requirements need to be fullfilled, but reliability is always a key element. The focus of this work is on integrated circuits processed in an advanced nm CMOS process. The evolution of the CMOS production process, from the conventional SiO<sub>2</sub> process to high-k metal-gate (HKMG) devices used in sub-45 nm technologies and the introduction of new device architectures such as FinFETs for sub-28 nm technologies, results in an increasing amount of reliability problems and is discussed in Sect. 1.4. Section 1.5 then discusses the basic activities needed to guarantee the reliable operation of a product or system. Also, the currently established IC design for reliability strategy is reviewed. Finally Sect. 1.6 presents the chapter conclusions.

#### 1.2 Reliability Engineering: A Brief History

Reliability is a popular concept and is also seen as a commendable attribute of a person or an object. Etymologically, the term stems from the Scottish word *raliabill* (rely+able, sixteenth century) (Saleh and Marais 2006). The first recorded usage of the word reliability, albeit referring to a person instead of an object, dates back to 1816 when it was introduced by poet Samuel Taylor Coleridge (Saleh and Marais 2006). In praise of his friend Robert Southey, Coleridge wrote:

1

2 1 Introduction

He inflicts none of those small pains and discomforts which irregular men scatter about them and which in the aggregate so often become formidable obstacles both to happiness and utility; while on the contrary he bestows all the pleasures, and inspires all that ease of mind on those around him or connected with him, with perfect consistency, and (if such a word might be framed) absolute reliability.

Today, the term is used extensively by the general public and the technical community. Web of science, for example, lists over 260,000 technical papers with 'reliability' as a keyword, while the popular search engine Google even returns over 218,000,000 hits (Saleh and Marais 2006). When referring to an object, reliability is now defined as the ability of a system or component to perform its required functions under stated conditions for a specified period of time. Further, between 1816 and now, many industrial evolutions such as the development of the first airplane in 1903 and the introduction of the Ford model T in 1908 as first mass produced car took place. All these inventions and technical ideas contributed to the rise of reliability engineering as a scientific discipline in the early 1950s (Fig. 1.1).

Probability theory and statistics are the essential ingredients without which reliability engineering could not have emerged. The theory of probability was established in 1654 by Blaise Pascal and Pierre de Fermat in the context of gaming and gambling. In 1812 Laplace introduced a series of techniques, related to probability and statistics, expanding their scope to various other problems such as demographics, population estimation and life insurance. Another essential enabler for the rise of reliability engineering as a technical discipline was the idea and practice of mass production as a means for cost reduction. To deal with quality issues in high-volume production,

**Fig. 1.1** Radar will win the war (Life Magazine 1944). Vacuum tubes, used as active components in World War II radar systems during the so-called wizard war, were the major source of system failure and initiated reliability engineering efforts in the early 1950s

first came statistical quality control in the late 1920s. Later, reliability engineering was introduced in the mid 1950s, to deal with the (un)reliability of the vacuum tube. The tube, which was invented by Lee de Forest in 1906, initiated the electronic revolution enabling a series of applications such as the radio, the television and the radar. In World War II, electronics played a critical role and contributed to the allies winning the 'wizard war'. The vacuum tube, an active element that was part of the radar systems, was however also the major source of equipment failure. This prompted the US Department of Defense (DoD) to initiate a series of studies to look into these failures after the war. In 1952, the advisory group on reliability of electronic equipment (AGREE) was jointly established between the DoD and the American electronics industry. Its mission was to recommend measures that would result in more reliable equipment, to help implement reliability programs in government and civilian agencies and to disseminate a better education on reliability. The first conference on quality control and reliability of electronics was held in 1954 and its proceedings evolved into a journal that is still being published: IEEE Transactions on Reliability. After the consolidation of the initial efforts addressing reliability issues in components, various branches with increased specialization were founded throughout the 1960s and 1970s. These branches include the development of improved statistical techniques (redundancy modeling, Bayesian statistics, etc.), modeling of physical causes of failure, prediction of reliability at a system level, etc.

The chain of events described above eventually led to the practical reliability engineering as it is known today. In the next sections, the focus is on the reliability requirements set by modern electronic systems and the problems involved with guaranteeing reliability in nanometer CMOS processes.

#### 1.3 Reliability of Electronic Systems

Many applications in our society today make use of advanced micro-electronic circuits. Depending on the application, each of these circuits has different requirements (see Fig. 1.2):

- 1. Consumer products such as cellphones, TVs and computers represent a huge market with a lot of competition. Here, a short time-to-market and a first-time-right approach are required to maintain or increase market share.

- Safety-critical applications require reliable circuit operation with a lifetime of ten to twenty years. Examples of such applications are a sensor interface used to monitor vital parameters in a car or biomedical products such as a pacemaker.

- 3. A third type of integrated circuits is used in very harsh environments. Circuits embedded in automotive products or airplanes, for example, typically have to endure large temperature variations and electromagnetic interference. Further, ICs used in more extreme applications such as satellites or sensors in nuclear reactors suffer from radiation effects. Each of these circuits, however, always needs to operate correctly.

4 1 Introduction

Fig. 1.2 Micro-electronic circuits are used in many applications. Each of these applications has specific needs. For consumer electronics the time to market is essential. Safety-critical products require very high-quality components. Circuits used in harsh environment need to operate in extreme conditions

Note how a circuit can belong to multiple categories at the same time. ICs for automotive products, for example, typically serve a large and competitive consumer market and are used in safety-critical and harsh environments at the same time. Designing these ICs is therefore very challenging.

Further, this vast market has lead to products with increasing functionality at a lower cost. To reduce production costs, the semiconductor industry continues to scale transistor devices to smaller nm CMOS technologies. To maintain the effective performance scaling, however, the oxide electric fields and current densities are increasing continuously. Advanced CMOS nodes are now reaching values where it is very challenging to guarantee—by the mere production and limiting the usage to predefined boundaries (e.g. maximum supply voltage)—reliable circuit operation over the intended product lifetime. In industry, reliability issues can therefore result in a stall of the production process or even a recall of already sold products. In 2011, for example, Intel was about to launch their Sandy Bridge processor when a potential reliability problem was detected (Clarke 2011). The problem, which was not spotted during extensive functional testing, was a gradual performance reduction and even total failure of the serial-ATA channels in about 5 % of the manufactured ICs. Another, unfortunately more common, problem with wireless electronic products is battery reliability. In 2009, HP recalled a large number of laptops after a number of incidents

with the battery that overheated and ruptured (Ogg 2009) due to a malfunctioning electronic protection circuit. A similar problem with overheating of Sony laptops was reported in 2010 (Lipka 2010).

The example cases above demonstrate that it is very difficult, even for a major company, to guarantee absolute reliability over a product lifetime. Nevertheless, even a limited number of product failures can already result in excessive warranty costs and severe brand damage. Further, electronic systems contain mixed-signal circuits with embedded high-performance analog or mixed-signal blocks and potential sensitive RF frontends. Although digital building blocks also suffer from aging effects, they are inherently more robust than analog circuits. Analog parts are often very sensitive to small variations and could be a bottleneck for circuit lifetime. Therefore, this work focuses on design for reliability of analog ICs. In the next section, nm CMOS reliability is discussed in more detail.

#### 1.4 Reliability in Nanometer CMOS

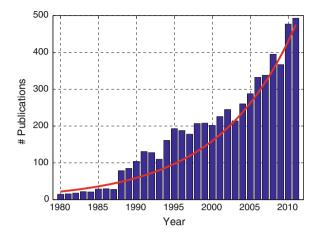

The exponential increase in the gate leakage current when scaling the gate oxide thickness of CMOS transistors, forced device engineers to introduce gate materials with a higher dielectric constant compared to traditional SiO<sub>2</sub> or SiON gate dielectrics. This allows further increase of the gate oxide capacitance while keeping the physical gate thickness sufficiently large (Degraeve et al. 2008). Unfortunately, the introduction of new materials and devices, combined with the further reduction of the lateral transistor dimensions, reduces circuit reliability. Also, more demanding mission profiles (e.g. higher operational temperatures, high currents and extreme lifetimes) and increasing constraints on time and money further increase the required levels of circuit reliability. As a result, device and interconnect reliability has become a major focus in the ITRS guidelines (International Technology Roadmap for Semiconductors 2011) (see Fig. 1.3). Further, as shown in Fig. 1.4, the increasing amount of reliability problems is also reflected in the number of publications on the subject, which has grown exponentially over the last three decades. Below, the major lifetime-limiting scaling factors are explained briefly. Details about each individual unreliability effect will be given in Chap. 2.

#### 1.4.1 Reduction of the Effective Oxide Thickness

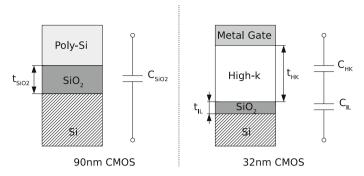

In the search for suitable high-k dielectrics, most research currently focuses on HfO-based or TiN-based materials. However, none of these dielectrics is compatible with Si. This incompatibility is solved by maintaining a very thin SiO<sub>2</sub> or SiON interfacial layer (IL) between the silicon substrate and the high-k material. Figure 1.5 depicts a schematic representation of a traditional 90 nm CMOS stack and a modern 32 nm

6 1 Introduction

| Table PIDS1 Process Integration Difficult Challenges |                                                                                                                                                            |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Near-Term 2011-2018                                  | Summary of Issues                                                                                                                                          |  |  |  |

| 1. Scaling Si CMOS                                   | Scaling planar bulk CMOS                                                                                                                                   |  |  |  |

|                                                      | Implementation of fully depleted SOI and multi-gate (MG) structures                                                                                        |  |  |  |

|                                                      | Controlling source/drain series resistance within tolerable limits                                                                                         |  |  |  |

|                                                      | Further scaling of EOT with higher $\kappa$ materials ( $\kappa > 30$ )                                                                                    |  |  |  |

|                                                      | Threshold voltage tuning and control with metal gate and high-k stack                                                                                      |  |  |  |

|                                                      | Inducing adequate strain in new structures                                                                                                                 |  |  |  |

| 2. Implementation of high-                           | Basic issues same as Si devices listed above                                                                                                               |  |  |  |

| mobility CMOS channel materials                      | High- $\kappa$ gate dielectrics and interface states $(D_{ii})$ control                                                                                    |  |  |  |

|                                                      | High-K gate dielectrics and interface states $(D_{tt})$ control  CMOS $(n$ - and $p$ -channel) solution with monolithic material integration               |  |  |  |

|                                                      | CMOS (n- and p-channel) solution with monortune material integration                                                                                       |  |  |  |

|                                                      | Epitaxy of lattice-mismatched materials on Si substrate                                                                                                    |  |  |  |

|                                                      | Process complexity and compatibility with significant thermal budget limitations                                                                           |  |  |  |

|                                                      | , , , , , , , , , , , , , , , , , , , ,                                                                                                                    |  |  |  |

| 3. Scaling of DRAM and SRAM                          | DRAM—                                                                                                                                                      |  |  |  |

|                                                      | Adequate storage capacitance with reduced feature size; implementing high-κ dielectrics                                                                    |  |  |  |

|                                                      | Low leakage in access transistor and storage capacitor, implementing buried gate type/saddle fin type FET                                                  |  |  |  |

|                                                      | Low resistance for bit- and word-lines to ensure desired speed                                                                                             |  |  |  |

|                                                      | Improve bit density and lower production cost in driving toward 4F <sup>2</sup> cell size                                                                  |  |  |  |

|                                                      |                                                                                                                                                            |  |  |  |

|                                                      | SRAM—                                                                                                                                                      |  |  |  |

|                                                      | Maintain adequate noise margin and control key instabilities and soft-error rate                                                                           |  |  |  |

|                                                      | Difficult lithography and etch issues                                                                                                                      |  |  |  |

| 4. Scaling high-density non-                         | Endurance, noise margin, and reliability requirements                                                                                                      |  |  |  |

| volatile memory                                      | Multi-level at < 20 nm nodes and 4-bit/cell MLC                                                                                                            |  |  |  |

|                                                      | Non-scalability of tunnel dielectric and interpoly dielectric in flash memory – difficulty of maintaining high gate coupling ratio for floating-gate flash |  |  |  |

|                                                      | Few electron storage and word line breakdown voltage limitations                                                                                           |  |  |  |

|                                                      | Cost of multi-patterning lithography                                                                                                                       |  |  |  |

|                                                      | Implement 3-D NAND flash cost effectively                                                                                                                  |  |  |  |

|                                                      | Solve memory latency gap in systems                                                                                                                        |  |  |  |

| Reliability due to material,                         | TDDB, NBTI, PBTI, HCI, RTN in scaled and non-planar devices                                                                                                |  |  |  |

| process, and structural changes,                     | Electromigration and stress voiding in scaled interconnects                                                                                                |  |  |  |

| and novel applications.                              | Increasing statistical variation of intrinsic failure mechanisms in scaled and non-planar devices                                                          |  |  |  |

|                                                      | 3-D interconnect reliability challenges                                                                                                                    |  |  |  |

|                                                      | Reduced reliability margins drive need for improved understanding of reliability at circuit level                                                          |  |  |  |

|                                                      | Reliability of embedded electronics in extreme or critical environments (medical, automotive,                                                              |  |  |  |

|                                                      | grid)                                                                                                                                                      |  |  |  |

**Fig. 1.3** Excerpt from the 2011 ITRS guideline on process integration, devices and structures. Reliability (indicated with *bold line*) is considered as a major problem in the near future

high-k metal-gate (HKMG) stack. For a transistor in inversion, the electric field  $E_{\rm SiO_2}$  over the SiO<sub>2</sub> layer in each stack can be written as:

$$E_{\rm SiO_2} = \frac{V_{\rm GS} - V_{\rm TH}}{\rm EOT} \tag{1.1}$$

with  $V_{\mathrm{TH}}$  the threshold voltage and EOT the effective oxide thickness:

Fig. 1.4 Evolution of the number of publications with keywords 'transistor reliability' as listed by IEEE Xplore

$$EOT_{90 \text{ nm}} = t_{SiO_2} \tag{1.2}$$

$$EOT_{32 \text{ nm}} = t_{IL} + \frac{\varepsilon_{SiO_2}}{\varepsilon_{HK}} t_{HK}$$

(1.3)

with  $t_{\rm SiO_2}$  the thickness of the SiO<sub>2</sub> oxide in a 90 nm technology (typically  $t_{\rm SiO_2} = 2.0 - 2.4$  nm),  $t_{\rm IL}$  the thickness of the SiO<sub>2</sub> interfacial layer in the 32 nm technology (typically  $t_{\rm IL} = 0.5 - 1$  nm) and  $t_{\rm HK}$  the thickness of the high-k layer in the 32 nm technology (typically  $t_{\rm HK} = 2 - 4$  nm).  $\varepsilon_{\rm SiO_2}$  and  $\varepsilon_{\rm HK}$  are the dielectric constants for SiO<sub>2</sub> ( $\varepsilon_{\rm SiO_2} \approx 3.9$ ) and the high-k dielectric respectively ( $\varepsilon_{\rm HK} \approx 30$ ). As a result, EOT<sub>32 nm</sub> is smaller than EOT<sub>90 nm</sub>, resulting in a larger electric field over the SiO<sub>2</sub>-interfacial layer of a HKMG technology compared to the electric field over the SiO<sub>2</sub> oxide in a traditional CMOS technology (i.e.  $E_{\rm SiO_2}$ ,  $_{\rm 32 nm} > E_{\rm SiO_2}$ ,  $_{\rm 90 nm}$ ) (Degraeve et al. 2008). Since most transistor degradation effects depend exponentially on this electric field, the introduction of high-k materials further reduces the maximum operating voltage to guarantee reliable circuit operation (Degraeve et al. 2008).

#### 1.4.2 Introduction of New Materials and Devices

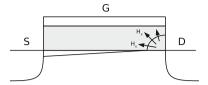

Transistor unreliability effects such as negative bias temperature instability (NBTI), temperature dependent dielectric breakdown (TDDB) and hot carrier injection (HCI) were in older  $SiO_2$  or SiON based technologies (i.e.  $\geq 65$  nm) considered as the most important aging effects. Both the NBTI and HCI effect generates traps at the substrate/dielectric interface (more details will be given in Chaps. 2 and 3). These traps affect transistor parameters such as the threshold voltage  $V_{TH}$ . With the introduction

8 1 Introduction

Fig. 1.5 Schematic representation of a traditional  $90 \,\mathrm{nm}$  CMOS  $\mathrm{SiO}_2$ -based stack (on the  $\mathit{left}$ ) and a  $32 \,\mathrm{nm}$  CMOS high-k metal-gate HfO-based stack (on the  $\mathit{right}$ )

of high-k materials and new device architecture such as FinFETs, a thin SiO<sub>2</sub> or SiON interfacial layer has however been maintained (see Fig. 1.5). Consequently, the substrate/dielectric interface does not change and NBTI and HCI remain a problem in HKMG technologies (Degraeve et al. 2008). Further, research has indicated the interfacial layer to be the major factor controlling breakdown in HKMG technologies (Bersuker et al. 2010). Therefore, models and principles previously developed to characterize breakdown in older technologies still apply in high-k technologies.

The PBTI effect, which is negligible in SiO<sub>2</sub> or SiON based technologies, has been found to become a lot worse in high-k technologies (Cho et al. 2010). Existing transistor failure mechanisms thus remain and even become worse with the introduction of high-k dielectrics in advanced nanometer CMOS nodes.

#### 1.4.3 Atomic-Scale Dimensions

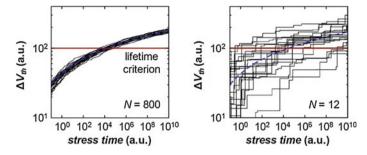

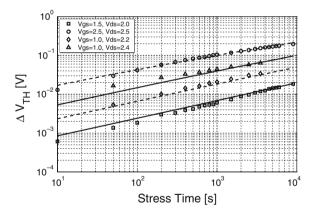

BTI and HCI effects in large micrometer-sized transistors are typically considered deterministic (see Chap. 3). The application of a given voltage stress on matched transistors therefore results in an identical shift of the transistor parameters (except for a statistical mismatch due to process variations). Scaling transistors down to nanometer dimensions, however, gradually has changed these deterministic effects into stochastically distributed failure mechanisms (Kaczer et al. 2010). At device level this results in a time-dependent shift of the transistor parameters (i.e.  $\Delta V_{\rm TH} = f(t)$ ) augmented with a time-dependent increase of the standard deviation on these parameters (i.e.  $\sigma(V_{\rm TH}) = g(t)$ ). After some time, initially matched transistors processed in ultrascaled nanometer CMOS technologies can therefore cause circuit failure resulting from increased time-dependent transistor mismatch. Also, electromigration in copper lines becomes worse due to a reduction of the cross sectional diameter of the interconnection wires with scaling (Zhang et al. 2010; International Technology Roadmap for Semiconductors 2011).

#### 1.4.4 Mission Profiles

Circuit environmental conditions and required performance tend to be stretched further with each technology generation. Sensor applications for automotive products, for example, need to function properly in temperatures exceeding 200 °C and applications such as base stations and solar cells must function reliably and almost continuously over a period of tens of years (International Technology Roadmap for Semiconductors 2011).

#### 1.4.5 Time and Money Constraints

The constraints on time and money are always increasing. This trends is combined with possible major technology changes and therefore poses a real challenge for reliability engineers to still guarantee reliable product operation. The speed of introduction of new materials and devices reduces the capability to build up knowledge on new failure mechanisms while, at the same time, failure rate requirements become more and more demanding (International Technology Roadmap for Semiconductors 2011). The probability of an unrecognized failure mechanism to make it into an end product is therefore increasing.

#### 1.5 Design for Reliability

The previous sections have discussed the ubiquitous presence of electronic systems in our modern society. Unfortunately, the device lifetime of the nm CMOS technology that enables this evolution reduces with each next technology generation. Some of these reliability problems can and are being solved at a device level. Already in the early 1980s, for example, alternative MOSFET structures with a graded drain junction or an offset gate structure (i.e. a lightly doped drain or LDD) to reduce the hot carrier degradation effects have been proposed (Takeda et al. 1982). A technology-based solution is however not always possible, especially since the focus of device engineers is typically on developing smaller and faster transistors with lower power consumption.

To cope with reliability problems during the design of a new product, a design for reliability (DFR) flow is used. Such a flow encompasses the entire set of tools supporting product and process design and ensuring that customer expectations for reliability are fully met throughout the life of the product. DFR relies on an array of reliability engineering tools along with a proper understanding of when and how to use these tools throughout the design cycle. DFR is of utmost importance to guarantee low warranty costs and high customer satisfaction. The technical problems with Microsoft's Xbox 360, in the early months after the console was introduced,

10 1 Introduction

illustrate this perfectly (Xbox 360 Technical Problems 2012). The problem, which has never been explained officially by Microsoft, caused a general hardware failure of the console and resulted in over a billion dollars in warranties to be paid. Understanding potential reliability issues, knowing how to identify them and being able to alleviate the problem is becoming more important with the increasing complexity of systems and its interactions.

The push for a more structured approach to guarantee product reliability is similar to the strive towards high-quality products in the 1980s. The latter led to successful processes such design for six sigma (Yang and El-Haik 2003). There is however a fundamental difference between quality and reliability. Quality control assures that each product sample works as designed right after production. Time-dependent effects are rarely taken into account here. Reliability, on the other hand, is about guaranteeing with a high probability that the product will perform its intended function without failure for a designated period of time and under specified conditions.

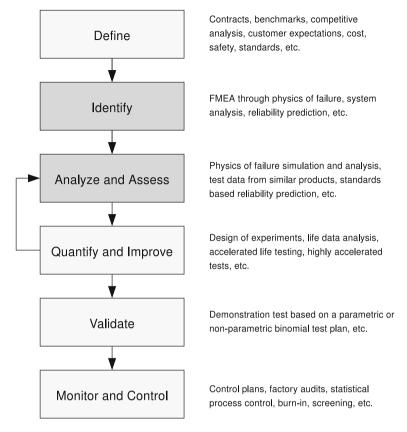

In order to control product reliability throughout the design process, Reliasoft proposed a number of key activities (Design for Reliability: Overview of the Process and Applicable Techniques 2012) define, identify, analyze and assess, quantify and improve, validate and monitor and control. The stages are depicted in Fig. 1.6 and typical tools and methods used in each stage are also given. The different activities are valid for any industrial production process, but here they are applied to the design and production of ICs. In the next sections, the different stages are briefly explained.

#### 1.5.1 Define

The purpose of this stage is to clearly and quantitatively define the reliability requirements and goals for a product, as well as the environmental and usage conditions. In industry, reliability specifications can come from various sources such as through contracts with customers, based on safety considerations, to remain competitive or to comply with a particular standard. The latter is particularly important in the automotive industry where the automotive electronics council (AEC) has established a series of standards for integrated circuits: the AEC-Q100 (stress qualification for ICs) and the AEC-Q200 (stress test qualification for passive components). These standards are mainly used in the US, but approved by many automotive electronics companies around the world. In Europe, the main standard used is the ISO 16750 series. Other commonly used IC reliability standards, also used for consumer or industrial applications, are MIL-STD 883, MIL-STD 750, JESD 47, JP001.01, JESD22A-108, JESD85, JESD74, JEP122 and EIAJ 4701-100. Table 1.1 summarizes the most important reliability-related requirements that are typically applied in different markets. As expected, specifications for the consumer market are clearly less demanding compared to industrial or automotive applications.

**Fig. 1.6** A general design for reliability (DFR) flow. Typical tools and methods used in each stage are also indicated. This work focuses on the design of reliable analog ICs therefore and studies an implementation of the second and third step of the above DFR flow (Design for Reliability: Overview of the Process and Applicable Techniques 2012)

#### 1.5.2 Identify

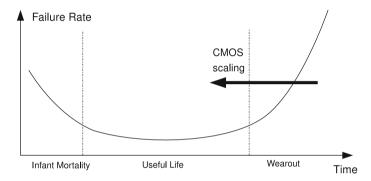

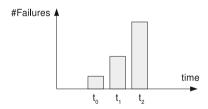

In this stage, possible reliability threats are identified. A failure mode effect analysis (FMEA) strategy can be used as a tool to quantify the risk associated with different failure effects. The failure rate or frequency with which an electronic system fails is typically represented using the so-called bathtub curve (see Fig. 1.7). Circuits that fail right after production are referred to as infant mortality failures. In IC design, these failures primarily result from process errors such as oxide defects, mask defects, contamination, bonding issues, solder defects, etc. Infant mortality failures typically happen within the duration of the product warranty and therefore have to be limited. During the useful life of the product, random defects and soft errors can result in an occasional circuit failure. Then, the product starts to wear out due to aging effects and

12 1 Introduction

|                         | Consumer          | Industrial    | Automotive            |

|-------------------------|-------------------|---------------|-----------------------|

| Operating temperature   | -5/0 °C −40/65 °C | -10 °C −70 °C | -40 °C −85/155 °C     |

| Lifetime (years)        | 1–5               | 5-10          | 15-20                 |

| Tolerated failure rates | <10 %             | <1%           | Target: zero failures |

| Humidity (%)            | 30-85             | 15-90         | 0 - 100               |

| Condensation            | Low               | Medium        | High                  |

| Temperature cycling     | Low               | Medium        | High                  |

| Altitude (km)           | 7–10              | 10-12         | 12-15                 |

| Vibration               | Low               | Medium        | High                  |

| Shock/bump              | Low               | Medium        | High                  |

| Sand/dust               | Low               | Medium        | High                  |

Table 1.1 Typical IC reliability requirements

Fig. 1.7 The *bathtub* curve represents the number of failures or the failure rate of a product over time

eventually every IC fails. The focus of this work is on the wearout stage, which sets in earlier with every new CMOS generation (also see Sect. 1.4) (Franco et al. 2010).

#### 1.5.3 Analyze and Assess

During the design phase, the product lifetime is estimated and expressed as the mean time to failure (MTTF). The MTTF also helps to compare different design concepts and can be used to identify design margins and to assess failure-resilient design strategies. To estimate the product lifetime (time to wearout), industry mainly uses accelerated stress tests on individual devices. Further, failure criteria are often chosen arbitrarily (e.g. a 10 % shift in  $I_D$ ) and the impact of device failure on the circuit level is typically not considered (Groeseneken et al. 2010). Circuit MTTF figures are therefore hard to estimate and rarely circuit specific. Designers are forced to use large design margins, ultimately limiting circuit performance or costing a large

area or power overhead, and even then uncertainty about the lifetime of a circuit remains. To solve these problems, reliability assessment needs to be done at design time, requiring:

- Accurate transistor compact models for all important transistor unreliability effects.

- Efficient circuit simulation techniques to i) analyze the reliability of a circuit and ii) to identify circuit reliability weak spots.

These are discussed further in this work for the aging-related effects in CMOS circuits.

#### 1.5.4 Quantify, Improve and Validate

During this stage, measurement results are used to verify the simulation results obtained from previous stages. This testing is typically done on prototype circuits using accelerated life tests (ALT). The results are analyzed, root causes for failure are identified and if necessary design changes are done and the tests are repeated. ALT was first developed in the 1960s to cope with the high-reliability requirements of the US space program. Old methods for product validation took too long times and were therefore no longer adequate to meet the short time-to-market demands. Therefore, a way to quickly identify product defects and to solve them effectively is the key issue for major manufacturers in the world. Today, HALT (highly accelerated life test) and HAST (highly accelerated stress test) are used to solve the problem. Starting in 1990, major manufacturers including HP, Dell, Cisco, Nortel, Tektronix and Motorola successfully employed a HALT approach to speed up the identification of design and production defects, with improvements being capable of lowering the cost of the warranty period, enhancing the reliability of the product and shortening the time to market. The failure modes identified by HALT, together with relevant information, can also be used as input for developing new products. HALT is done with a chamber, as depicted in Fig. 1.8, enabling gradually increased voltage and temperature stressing such as high and low thermal cycling, combined stress, power switch cycling and voltage and frequency margin test. If a reliability problem is detected, design changes are needed and the activities described above are repeated until the product is considered to be acceptable. Further, extra variations introduced by the manufacturing process also need to be taken into account and if necessary design modifications are required to account for this. After this stage, the product is ready for volume production.

#### 1.5.5 Monitor and Control

Once a product is in production, the process is monitored to assure that process variations are kept under control and that reliability is still guaranteed. Burn-in techniques

14 1 Introduction

Fig. 1.8 A highly accelerated life test (HALT) chamber enables the reliability testing of electronic circuits at elevated voltages and temperatures

are used to prevent infant mortality failures due to manufacturing-related problems (Vassighi et al. 2004). Further, continuous monitoring and field data analysis can help to observe the behavior of the circuit in actual use conditions and to gain knowledge for further improvements.

#### 1.6 Conclusions

This introductory chapter has discussed the importance of long- and medium-term reliability in various application domains. Circuits designed in nanometer CMOS technologies suffer more than ever from transistor aging effects. Therefore a design for reliability strategy is needed. The different stages of such a DFR flow have been discussed and the current industrial approach has been reviewed. Early life failures due to defects related to the production process are eliminated with careful process control and circuit burn-in testing. Wearout of ICs, however, is typically only evaluated at the device level and a lack of circuit-level evaluation and assessment results in the use of large design guardbands, costing a large area and/or power overhead. The focus of this work is on the development of transistor compact models and simulation methods for analog circuit lifetime analysis in nm CMOS. Further, the goal of this work is also to assess the impact of these aging effects on analog circuits.

## Chapter 2 CMOS Reliability Overview

#### 2.1 Introduction

For over four decades, scientists have been scaling devices to increasingly smaller feature sizes (Lewyn et al. 2009; International technology roadmap for semiconductors 2011). This trend is driven by a seemingly unending demand for ever-better performance and by fierce global competition. The steady CMOS technology down-scaling is needed to meet requirements on speed, complexity, circuit density, power consumption and ultimately cost required by many advanced applications. However, going to these ultra-scaled CMOS devices also brings some drawbacks.

This chapter discusses the most important effects designers have to deal with in order to manufacture reliable integrated circuits in nanometer CMOS processes. The intent of this chapter is not to give an in-depth description of the physics behind each failure mechanism, but to provide the reader with a basic understanding of the most important unreliability effects and how these effects evolve with technology. First, Sect. 2.2 briefly outlines how various unreliability effects came into play in the course of history. Next, Sect. 2.3 reviews the most important spatial unreliability effects in modern CMOS technologies. These effects are related to process variations and are visible right after production. A difference is made between systematic and random effects. Time-dependent unreliability effects are then discussed in Sect. 2.4. These effects are divided into aging and transient effects.

#### 2.2 The Origin of CMOS Unreliability

Device reliability was first studied in the early sixties, when increasingly complex integrated systems were developed and fabricated. Conferences such as the first international reliability physics symposium (IRPS 1962, Chicago) were the first attempts to bring engineers and scientists together from all over the world to study the physics behind various failure effects (Physics of failure in electronics 1962).

Fig. 2.1 Photomicrograph of an early silicon mesa transistor on which the emitter bond has separated due to 'purple plague' (Phillips et al. 1962). This phenomenon, also known as 'purple death', was an important reliability problem in the late 1960s and the early 1970s. An intermetallic reaction between the golden bond wires and the aluminum bond pads formed a brittle bright purple compound of AuAl<sub>2</sub> which led to the creation of voids in the metal lattice

During the 1970s, effects such as corrosion, bonding issues (e.g. the 'purple plague' as depicted in Fig. 2.1) and ionic contamination were the most common causes of circuit failure. All these issues were however related to the way how integrated circuits were packaged and mounted on a printed circuit board (PCB). Only in the late seventies and early eighties the first real integrated circuit reliability issues became visible. Oxide thickness scaling increased the gate-oxide electric field, and transistor wearout effects such as hot carrier injection (HCI) started to affect device performance within the lifetime of a circuit (Takeda et al. 1983; Hu et al. 1985). Initially, the application of an arbitrary voltage stress resulted in an identical parameter shift for matched devices. Therefore these temporal unreliability effects were at first considered as deterministic. However, when the oxide dielectric reached atomic-scale dimensions, this resulted in the first stochastic temporal unreliability effect: timedependent dielectric breakdown (Solomon 1977). Further, matched devices were, in the early eighties, considered identical in terms of electrical performance. In the second half of that decade, however, when device dimensions entered the nanometer scale, stochastic errors and variations at atomic level became apparent at device level and sensitive analog circuits were the first to suffer from process variability effects (Lakshmikumar et al. 1986; Pelgrom et al. 1989). Device mismatch became a big issue (especially analog) designers had to deal with in order to guarantee good accuracy and high yield.

To overcome scaling limitations of devices fabricated in ultra-scaled CMOS processes, changes in device structures, processing materials and processing conditions have been introduced. These changes have drastically increased the complexity of nanometer CMOS technologies. Examples of these new techniques include:

| Year | Lg (nm) | V <sub>DD</sub> (V) | V <sub>TH</sub> (V) | EOT (nm)  | E <sub>ox</sub> (MV/cm) |

|------|---------|---------------------|---------------------|-----------|-------------------------|

| 1995 | 350     | 3.3                 | 0.58-0.70           | 10.0-12.0 | 2.17–2.72               |

| 1998 | 250     | 1.8-2.5             | 0.47 - 0.52         | 6.0-7.0   | 1.83-3.38               |

| 2003 | 180     | 1.8                 | 0.39-0.43           | 4.5-5.5   | 2.49-3.13               |

| 2001 | 130     | 1.2                 | 0.35-0.40           | 3.5-4.0   | 2.00-2.43               |

| 2004 | 90      | 1.0-1.2             | 0.25 - 0.40         | 1.6-3.0   | 2.00-5.93               |

| 2007 | 65      | 1.0-1.2             | 0.20 - 0.35         | 1.5-2.0   | 3.25-6.66               |

| 2009 | 45      | 1.0-1.1             | 0.20 - 0.35         | 1.0-1.4   | 4.64-9.00               |

| 2011 | 32      | 0.9-1.0             | 0.20-0.35           | 0.8-1.1   | 5.00-10.0               |

**Table 2.1** Evolution of nanometer CMOS characteristics

(Iwai 1999; Bult 2000; Bravaix et al. 2009; Wu et al. 2009; Europractice 2012; International technology roadmap for semiconductors 2011)

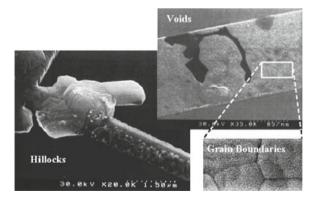

strained silicon channels to increase the transistor drive current, the introduction of high-k oxides and metal gates to allow further gate oxide scaling combined with reduced gate leakage, and Cu-interconnect with low-k dielectrics to ensure lower RC-delays (Horstmann et al. 2009; International technology roadmap for semiconductors 2011). However, the introduction of these new materials also increased the impact of already existing but before then unimportant aging effects, such as electromigration (EM) and negative bias temperature instability (NBTI), and even created new problems such as positive bias temperature instability (PBTI) (Lewyn et al. 2009; Groeseneken et al. 2010). Table 2.1 gives an overview of typical technology parameters for the most recent CMOS nodes. The table clearly shows how the average oxide electric field increases with each new technology node, aggravating all transistor wearout effects. All of these phenomena can have a large impact on the reliability of a circuit, right after production or during its operational lifetime. Therefore, a good understanding of the impact of each effect on the electrical behavior of a single transistor and eventually on the performance of an entire circuit is mandatory.

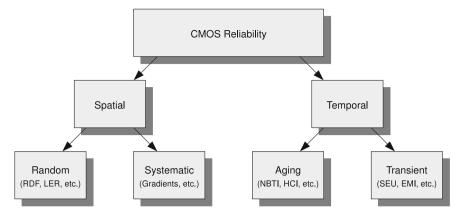

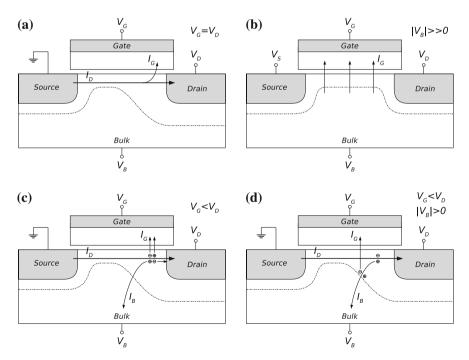

Figure 2.2 illustrates how nanometer CMOS reliability issues can be categorized into spatial and temporal unreliability effects. Spatial unreliability effects are immediately visible right after production and are fixed in time. Spatial unreliability effects can be random (e.g. random dopant fluctuations (RDF), line edge roughness (LER), etc) or systematic (e.g. gradient effects, etc.). The effects depend on the circuit layout, the neighboring environment, process conditions and the impact the geometry and structure of the circuit and can lead to yield loss. This yield loss can be functional or parametric, i.e. resulting in malfunctioning circuits or circuits with degraded performance respectively. Temporal unreliability effects, on the other hand, are timevarying and change depending on operating conditions such as the operating voltage, temperature, switching activity, presence and activity of neighboring circuits. A difference is made between wearout or aging effects (e.g. hot carrier injection (HCI), NBTI, etc.) and transient effects (e.g. electromagnetic interference (EMI), single event upsets (SEU), etc.). In the following sections, these effects are discussed in more detail.

**Fig. 2.2** A CMOS circuit can fail from spatial or temporal unreliability effects. The former are visible right after production and can be random or systematic. The latter become a potential problem during the operational lifetime of the circuit and present themselves as an aging effect or a transient effect

#### 2.3 Spatial Unreliability

Spatial unreliability or process variability is an increasing problem in nanometer CMOS IC production. The problem results from the increasing complexity needed to fabricate nanometer CMOS devices, combined with the scaling towards atomistic device dimensions (<180 nm CMOS). Typically, parametric yield is used as a metric to express the impact of these effects on the performance of the circuit right after production. A high yield implies low spatial unreliability.

Two major sources of process variability are distinguished: local or intradie and global or interdie effects. Local variability results in parametric variations of identically designed transistors across a short distance, typically within the same circuit. This is also referred to as device mismatch. Global variability refers to variations between devices that are separated by a long distance or that are fabricated at a different time. Typically global variability is variability from die to die, wafer to wafer or lot to lot. Global variability causes a shift in the mean value of design parameters such as channel length or doping density. Since most spatial unreliability problems result from local variability effects, global variability is not discussed here. Local variability originates from systematic and random reliability effects. The former includes variability caused by optical proximity correction, layout-induced strain and well-proximity effects. The latter includes random dopant fluctuation (RDF) effects, line edge and width roughness (LER and LWR), fixed charges in the gate dielectric and interface roughness. Systematic variability is typically addressed through

<sup>&</sup>lt;sup>1</sup> Parametric circuit failures are related to process variations and are circuits that do function but with a performance outside the desired range. Catastrophic circuit failures result from process errors or defects and are described by the functional yield. The latter are not covered in this work.

careful layout design, compensating circuit techniques and with advanced manufacturing flows. Solving random variability issues, on the other hand, requires innovative process and design techniques and accurate device models. For technology generations below 90 nm CMOS, the impact of random variability is becoming increasingly important (Lewyn et al. 2009). Both the systematic and random variability effects are discussed in more detail in the next sections.

#### 2.3.1 Systematic Effects

While most device-related sources of spatial unreliability are random, a large fraction of the variation of the interconnect is a function of layout characteristics (i.e. design dependent). These sources of variability have a large systematic component. With the aggressive scaling to smaller feature sizes, this component has become larger primarily due to resolution limitations. The inability to scale the wavelength of the light source for lithography has led to an increase of systematic variations, especially in circuit areas with high interconnect and device density (Agarwal and Nassif 2007). To mitigate these problems, a lot of research has gone into more advanced manufacturing flows such as double-patterning technologies (DPT), optical-proximity correction (OPC), extreme ultraviolet lithography (EUVL) and into design techniques such as the use of extremely regular circuit layout (Strojwas 2011).

#### 2.3.2 Random Effects

Random spatial unreliability results from physical phenomena such as random dopant effects, line edge and width roughness, fixed charges in the gate dielectric and oxide thickness variation resulting from interface roughness (Agarwal and Nassif 2007). Random effects typically affect the mismatch between closely spaced identically designed devices. At device level these effects mainly result in variations of the gate length (L), the threshold voltage ( $V_{\rm TH}$ ) and the current factor ( $\beta$ ) (Zhao et al. 2007), and they can to first order be modeled with Pelgrom's model (Pelgrom et al. 1989):

$$\sigma(\delta V_{\rm TH}) \approx \frac{A_{\rm VTH}}{\sqrt{WL}}$$

(2.1)

where  $\sigma(\delta V_{\text{TH}})$  is the standard deviation on the threshold voltage mismatch between two identically sized transistors, WL is the size of the active area of one transistor and  $A_{\text{VTH}}$  is a technology-dependent constant commonly expressed in mV  $\mu$ m.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> Pelgrom's model expresses the standard deviation on the *difference* between the threshold voltages of two matched transistors. The standard deviation on the threshold voltage of a single transistor can be found by dividing  $A_{\text{VTH}}$  by  $\sqrt{2}$ .

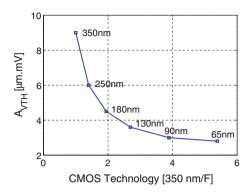

Fig. 2.3 Measured  $A_{\rm VTH}$  values for minimum-length pMOS devices as a function of 350 nm over the minimum feature size F. Extrapolating the curve, significant improvements are not expected beyond the 65 nm technology node. Data taken from Lewyn et al. (2009)

The actual relationship is more complex than (2.1) (Hong et al. 2011). Currently, IC foundries supply Monte-Carlo (MC) simulation models to accurately simulate the impact of process variations on transistor and circuit performance. Pelgrom's formula is however still used by designers for initial circuit design. It is therefore interesting to look at  $A_{\rm VTH}$  trends in advanced technology nodes (see Fig. 2.3). From Fig. 2.3 it is clear how  $A_{\rm VTH}$  does not improve much beyond the 90 nm technology node. Where for older technologies (>180 nm) transistor matching was primarily determined by lithographic accuracy that scaled well with technology, other factors that do not scale well are now taking over (Lewyn et al. 2009). These effects are discussed in the following sections.

#### **Random Dopant Fluctuations**

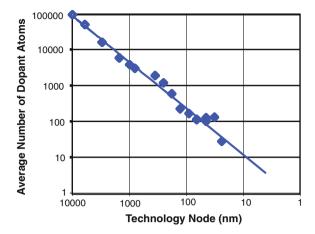

Variations of device parameters such as the transistor  $V_{\rm TH}$  partly result from fluctuations in the amount and location of dopant atoms in the transistor channel (Takeuchi et al. 2007; Kuhn et al. 2008). Since the number of dopant atoms in the channel of scaled transistors is always decreasing, the impact of the variation associated with the atoms increases. Figure 2.4 illustrates the decreasing average number of dopant atoms as a function of technology. Note how the number of dopants decreases by almost three orders of magnitude when going from a 1  $\mu$ m (with around 1e4 dopant atoms) to a 32 nm technology (with less than 100 dopant atoms). Random dopant fluctuations (RDF) are assumed to be the major contributor to device mismatch of identically designed devices. For example, in (Kuhn 2007) it is shown how the simulated RDF is responsible for around 65% of the total NMOS  $V_{\rm TH}$  variation of a 65 nm CMOS technology. Similar results were obtained for a 45 nm PMOS transistor, where RDF was responsible for 60% of the  $\sigma(V_{\rm TH})$ . The effect of RDF on the transistor threshold variation is frequently represented by (Stolk et al. 1998):

$$\sigma(V_{\rm TH}) \propto \frac{t_{\rm ox}}{\varepsilon_{\rm ox}} \frac{\sqrt[4]{N}}{\sqrt{W_{\rm eff} L_{\rm eff}}}$$

(2.2)

Fig. 2.4 Average number of dopant atoms in the channel of a transistor as a function of the technology node (Kuhn et al. 2008)

with  $t_{\rm ox}$  the gate oxide thickness,  $\varepsilon_{\rm ox}$  the oxide permittivity, N the number of channel dopants and  $W_{\rm eff}$  and  $L_{\rm eff}$  the transistor effective width and length. Equation (2.2) shows that  $V_{\rm TH}$  matching improves with technology scaling (both  $t_{\rm ox}/\varepsilon_{\rm ox}$  and N reduce with smaller feature sizes). However, the device area ( $W_{\rm eff}L_{\rm eff}$ ) also decreases with each new technology generation. Therefore the net result of RDF is a significant increase in process variability for scaled CMOS technologies.

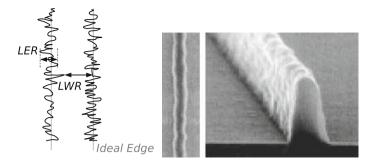

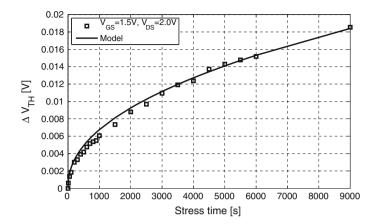

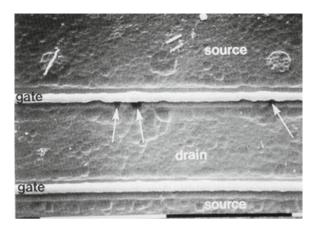

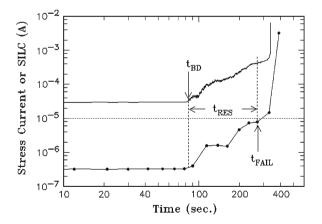

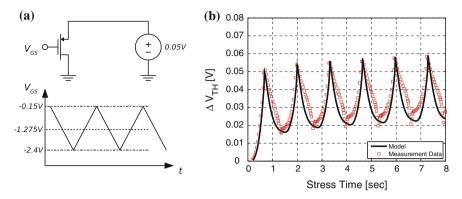

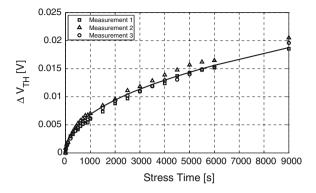

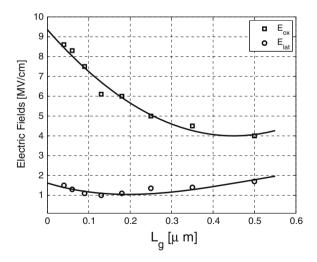

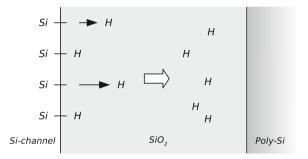

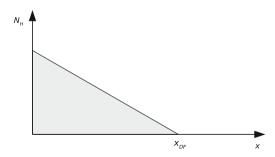

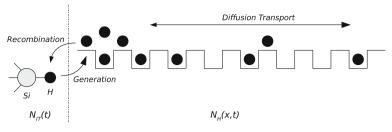

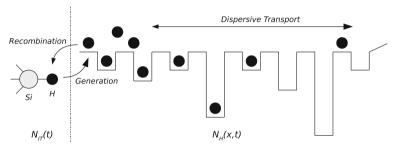

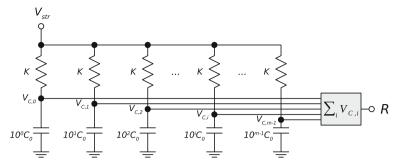

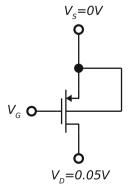

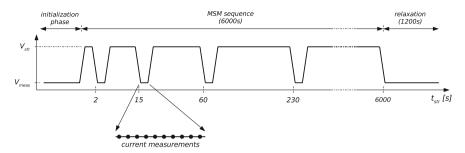

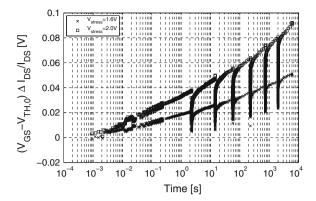

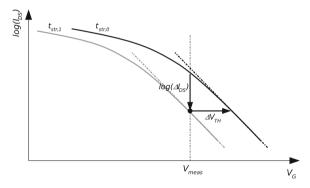

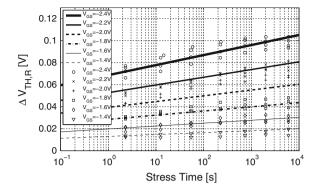

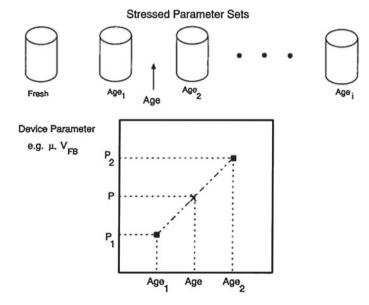

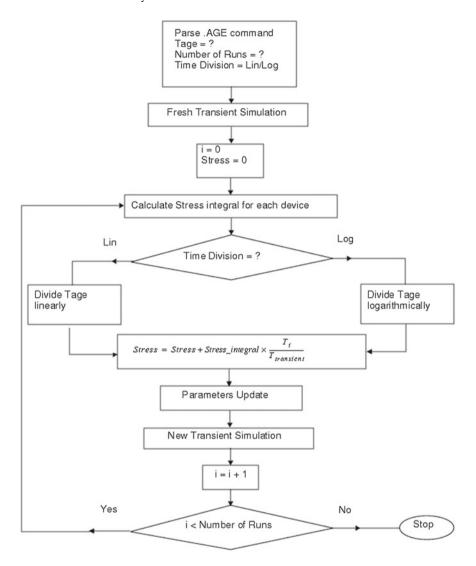

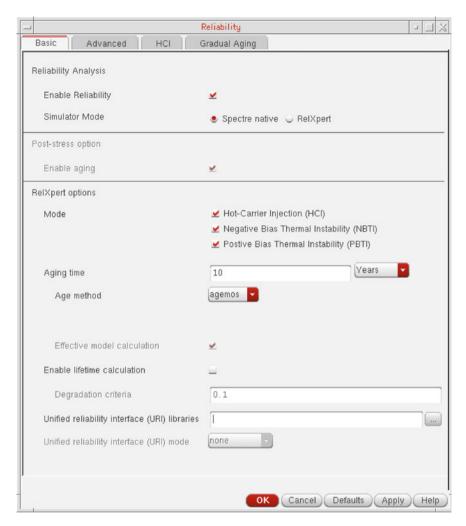

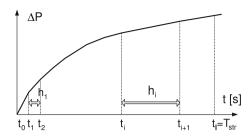

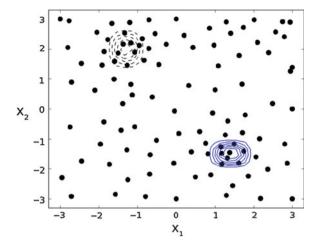

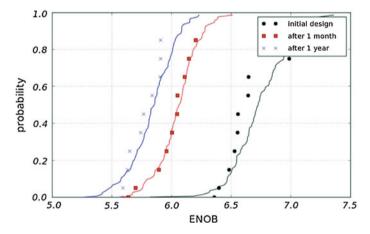

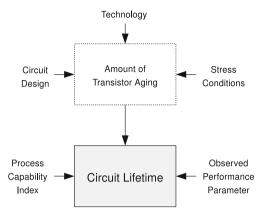

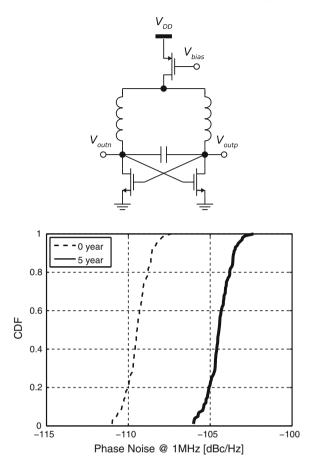

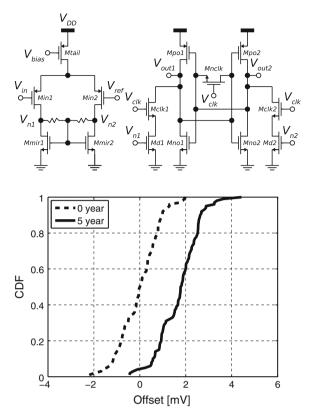

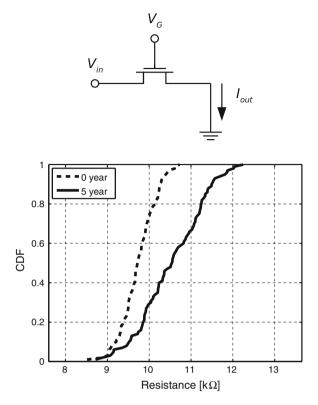

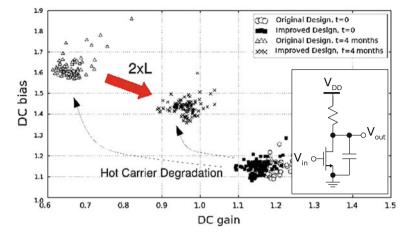

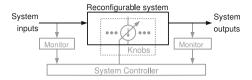

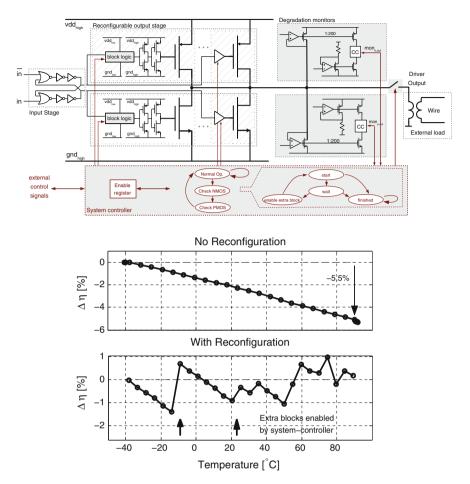

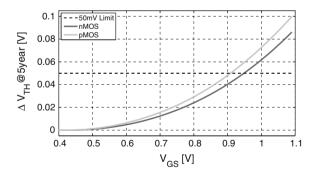

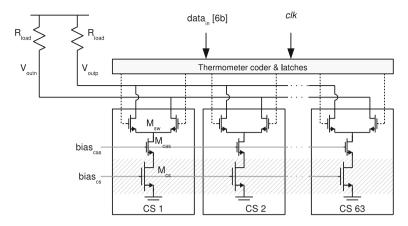

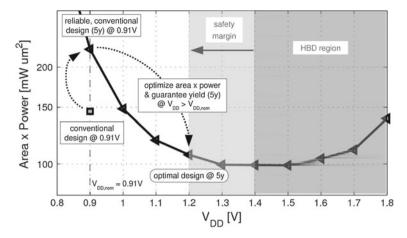

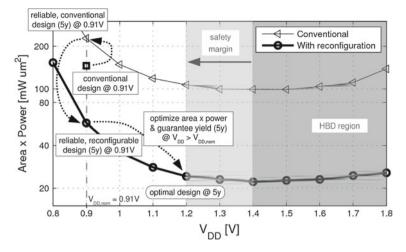

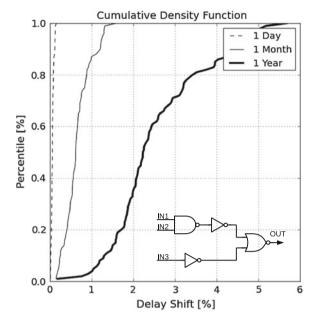

#### Line Edge/Width Roughness