# Master thesis

## Piotr Rymaszewski

major: **technical physics** specialisation: **solid state physics**

# Development of 12-bit ADC for particle physics applications using deep-submicron CMOS technology

Supervisor: dr hab. inż. Marek Idzik

Cracow, August 2013

Aware of criminal liability for making untrue statements I declare that the following thesis was written personally by myself and that I did not use any sources but the ones mentioned in the dissertation itself.

(Signature)

The subject of the master thesis and the internship by Piotr Rymaszewski, student of 5th year major in technical physics, specialisation in solid state physics

The subject of the master thesis: **Development of 12-bit ADC for particle physics applications using deep-submicron CMOS technology**

Supervisor: Dr hab. inż. Marek Idzik Reviewer: Dr inż. Krzysztof Świentek A place of the internship: WFiIS AGH, Kraków

#### Programme of the master thesis and the internship

- 1. Discussion with the supervisor on realization of the thesis.

- 2. Collecting and studying the references relevant to the thesis topic.

- 3. The internship:

- Design and simulations of integrated analog-to-digital converter.

- Design of physical layout of circuit.

- 4. Ordering and first analysis of the obtained results.

- 5. Final analysis of the results obtained, conclusions discussion with and final approval by the thesis supervisor.

- 6. Typesetting the thesis.

Dean's office delivery deadline: August 2013

(signature of Head of Department)

(Supervisor's signature)

Supervisor's review

Reviewer's review

Author wishes to express sincere gratitude to his supervisor dr hab. inż. Marek Idzik who provided invaluable support and guidance throughout the research. Special thanks are also due to dr Jan Kapłon, Dominik Przyborowki, Jakub Moroń and Michał Dwużnik whose knowledge and help were vital to the author.

# Table of contents

## Page

| In       | trod              | uction                                                                                                      |                                                                                                               | nts       2         :iments       4                                                                                    |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1        | Hig               | h Ener                                                                                                      | gy Physics experiments                                                                                        | <b>2</b>                                                                                                               |

|          | 1.1               | Physic                                                                                                      | s in HEP experiments                                                                                          | 2                                                                                                                      |

|          | 1.2               | Presen                                                                                                      | t and future HEP experiments                                                                                  | 4                                                                                                                      |

|          | 1.3               | Read-o                                                                                                      | out electronics                                                                                               | 6                                                                                                                      |

|          | 1.4               | Motiva                                                                                                      | tions for this work                                                                                           | 7                                                                                                                      |

| <b>2</b> | Ove               | rview                                                                                                       | of analog-to-digital converters                                                                               | 9                                                                                                                      |

|          | 2.1               | Basic o                                                                                                     | definitions                                                                                                   | 9                                                                                                                      |

|          |                   | 2.1.1                                                                                                       | Static parameters                                                                                             | 10                                                                                                                     |

|          |                   | 2.1.2                                                                                                       | Dynamic parameters                                                                                            | 13                                                                                                                     |

|          | 2.2               | Overvi                                                                                                      | ew of ADC architectures                                                                                       | 16                                                                                                                     |

|          |                   | 2.2.1                                                                                                       | Oversampling ADC                                                                                              | 17                                                                                                                     |

|          |                   | 2.2.2                                                                                                       | Nyquist rate ADC                                                                                              | 18                                                                                                                     |

|          |                   |                                                                                                             |                                                                                                               |                                                                                                                        |

| 3        | SAI               | R ADC                                                                                                       | 2 – algorithm variants and building blocks general considerations                                             | 22                                                                                                                     |

| 3        | <b>SAI</b><br>3.1 |                                                                                                             | C – algorithm variants and building blocks general considerations<br>ts of successive approximation algorithm | <b>22</b><br>22                                                                                                        |

| 3        |                   |                                                                                                             |                                                                                                               |                                                                                                                        |

| 3        |                   | Varian                                                                                                      | ts of successive approximation algorithm                                                                      | 22                                                                                                                     |

| 3        |                   | Varian<br>3.1.1                                                                                             | ts of successive approximation algorithm                                                                      | 22<br>24                                                                                                               |

| 3        |                   | Varian<br>3.1.1<br>3.1.2                                                                                    | ts of successive approximation algorithm                                                                      | 22<br>24<br>25                                                                                                         |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3                                                                           | ts of successive approximation algorithm                                                                      | 22<br>24<br>25<br>27                                                                                                   |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                  | ts of successive approximation algorithm                                                                      | 22<br>24<br>25<br>27<br>29                                                                                             |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                         | ts of successive approximation algorithm                                                                      | <ul> <li>22</li> <li>24</li> <li>25</li> <li>27</li> <li>29</li> <li>30</li> </ul>                                     |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                | ts of successive approximation algorithm                                                                      | <ul> <li>22</li> <li>24</li> <li>25</li> <li>27</li> <li>29</li> <li>30</li> <li>32</li> </ul>                         |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7                                       | ts of successive approximation algorithm                                                                      | <ul> <li>22</li> <li>24</li> <li>25</li> <li>27</li> <li>29</li> <li>30</li> <li>32</li> <li>34</li> </ul>             |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8                              | ts of successive approximation algorithm                                                                      | <ol> <li>22</li> <li>24</li> <li>25</li> <li>27</li> <li>29</li> <li>30</li> <li>32</li> <li>34</li> <li>37</li> </ol> |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9<br>3.1.10           | ts of successive approximation algorithm                                                                      | 22<br>24<br>25<br>27<br>29<br>30<br>32<br>34<br>37<br>40                                                               |

| 3        |                   | Varian<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9<br>3.1.10<br>3.1.11 | ts of successive approximation algorithm                                                                      | 22<br>24<br>25<br>27<br>29<br>30<br>32<br>34<br>37<br>40<br>43                                                         |

|    |       | 3.2.2 Split DACs comparison                                                | 52        |

|----|-------|----------------------------------------------------------------------------|-----------|

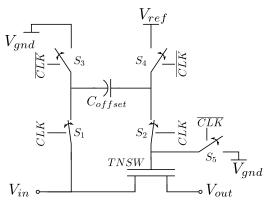

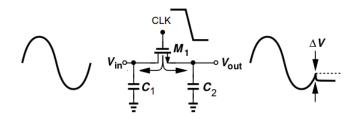

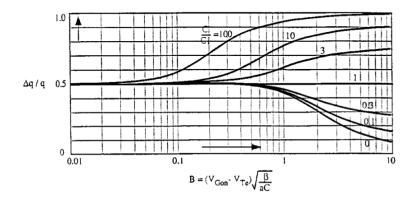

|    | 3.3   | Sampling switch                                                            | 53        |

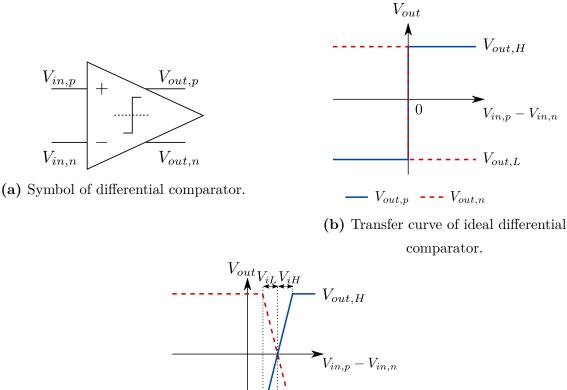

|    | 3.4   | Comparator                                                                 | 56        |

|    | 3.5   | SAR logic                                                                  | 60        |

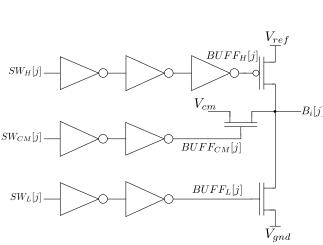

|    | 3.6   | DAC switches                                                               | 61        |

| 4  | Des   | ign of 12-bit SAR ADC                                                      | 32        |

|    | 4.1   | DAC                                                                        | 63        |

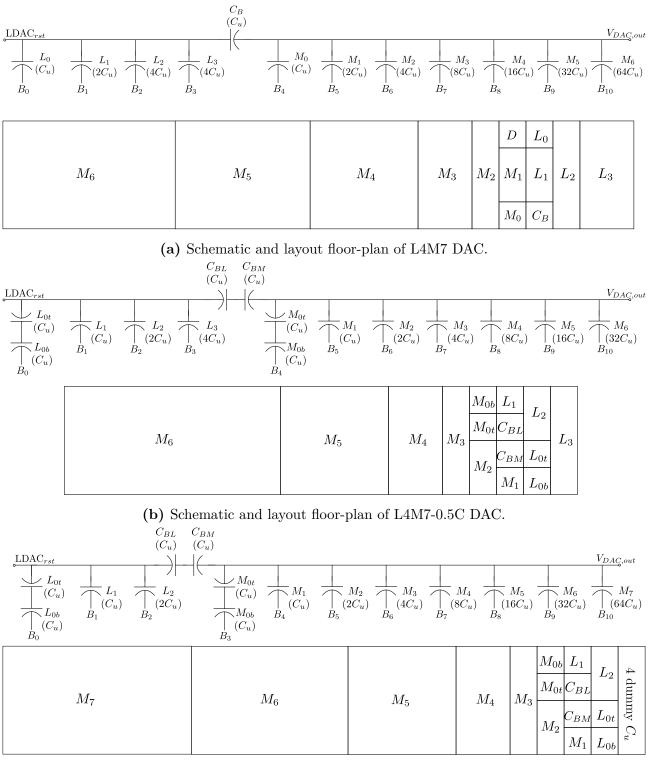

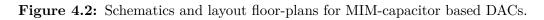

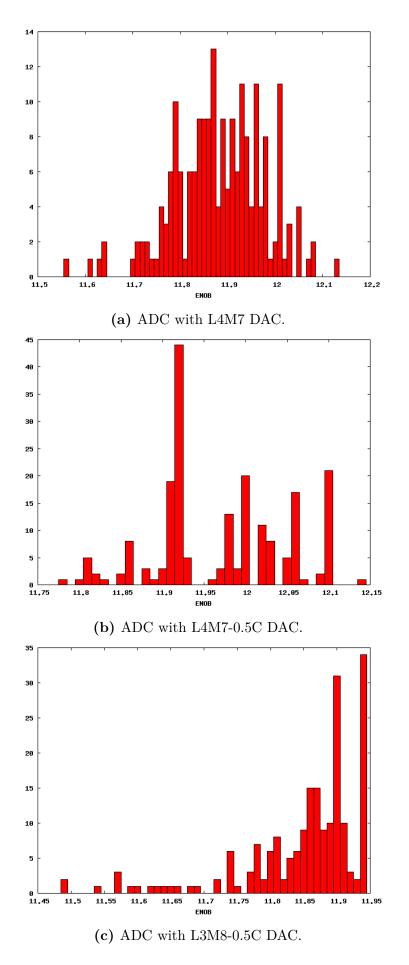

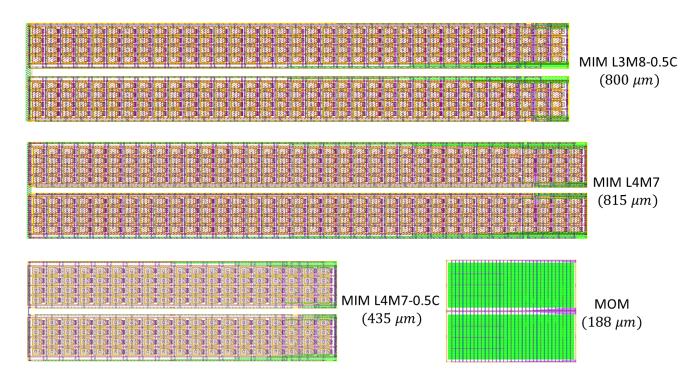

|    |       | 4.1.1 MIM capacitor DACs                                                   | 63        |

|    |       | 4.1.2 MOM-capacitor based DAC                                              | 67        |

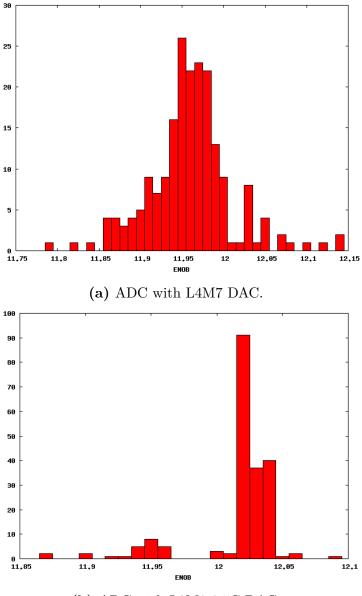

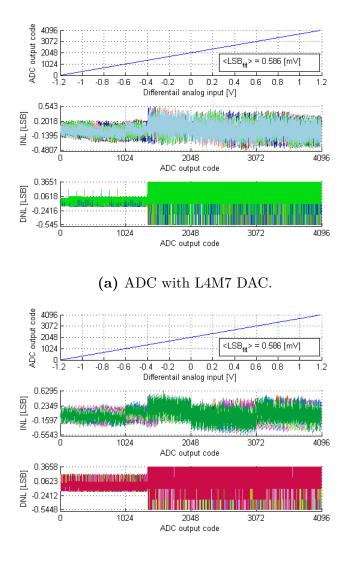

|    |       | 4.1.3 Comparison of MCS and EMCS algorithms influence on DAC's performance | 71        |

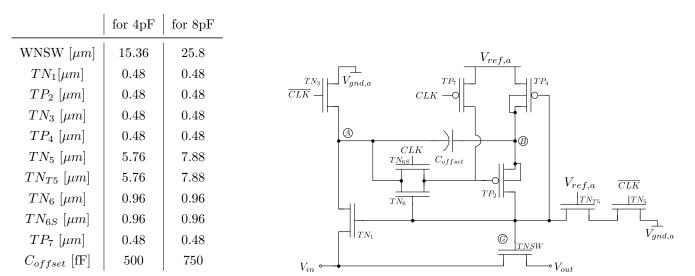

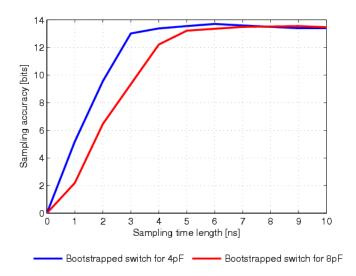

|    | 4.2   | Bootstrapped switch                                                        | 73        |

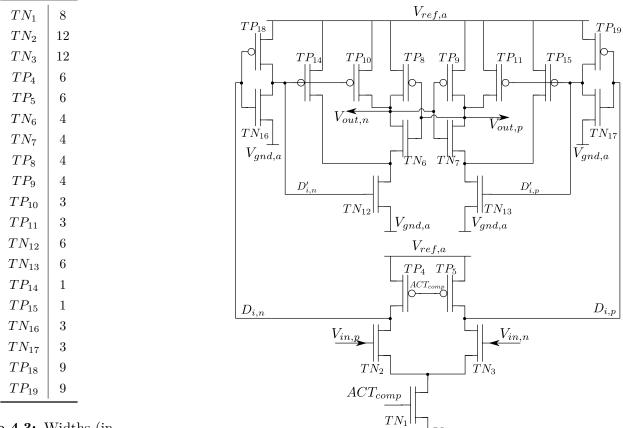

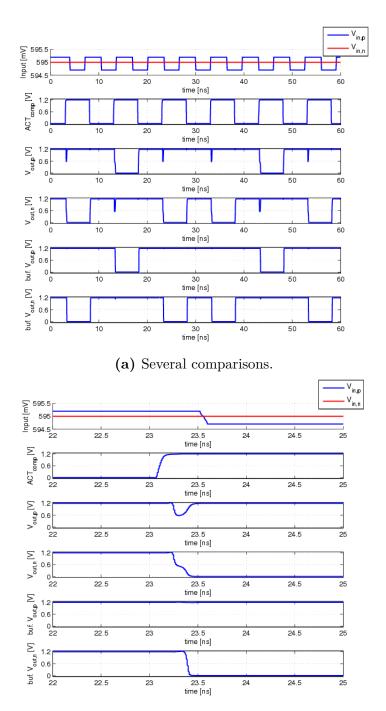

|    | 4.3   | Comparator                                                                 | 75        |

|    | 4.4   | DAC switches                                                               | 78        |

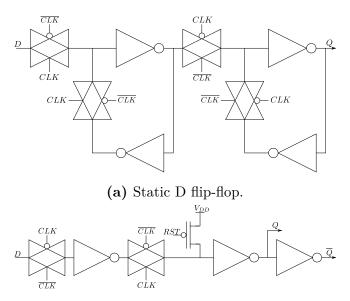

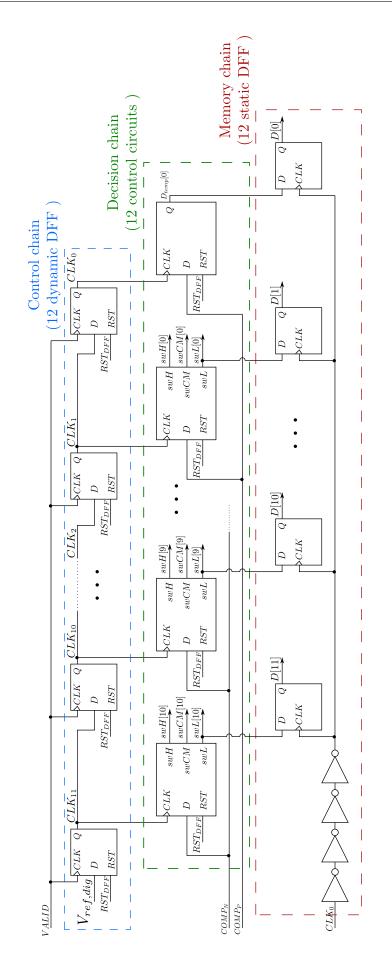

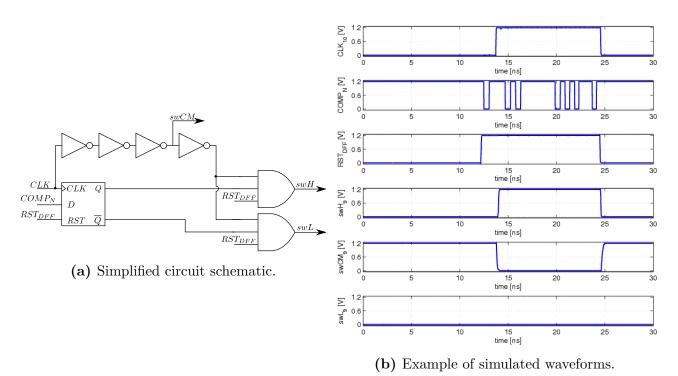

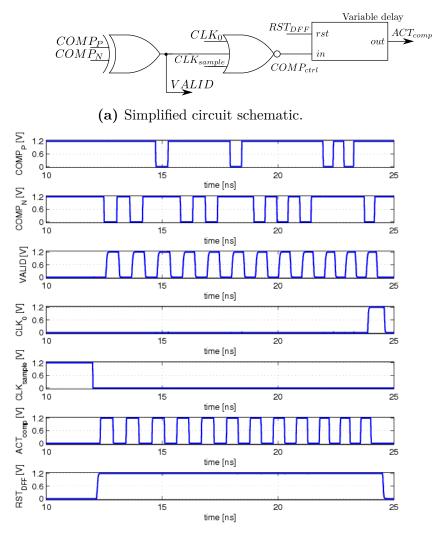

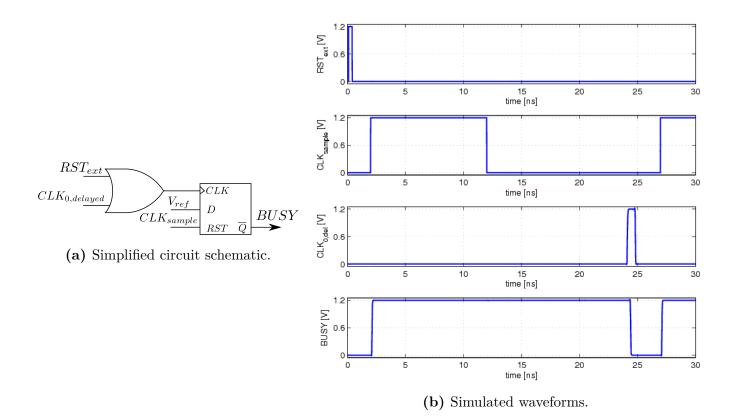

|    | 4.5   | SAR MCS Logic                                                              | 79        |

|    | 4.6   | Performance of designed ADC                                                | 86        |

| Su | mma   | ary                                                                        | 89        |

| Aŗ | open  | dix A Energy cost of DAC switching for 3-bit classical ADC                 | 91        |

| A  | open  | dix B Logical effort method                                                | 95        |

| A  | open  | dix C Matlab code for SAR algorithms energy consumption calculation §      | <b>}9</b> |

| Li | st of | Figures                                                                    | 07        |

| Li | st of | Tables                                                                     | 11        |

| Bi | bilog | grapy $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                     | 15        |

# Introduction

Current times are very exciting for High Energy Physics (HEP) – results from experiments carried out at Large Hadron Collider (LHC), the biggest particle collider up to date, state that a particle very similar to Higgs boson have been found. This is a discovery of a great magnitude, since it delivers long sought after informations about particle interactions and further confirms that Standard Model, theory currently used to describe particles and their behaviour, is correct. In light of this discovery future HEP experiments are being planned to determine, with precision greater than achievable by LHC, exact nature and properties of this newly found particle. To reach these goals new colliders and detectors will require electronics capable of delivering more precise data than electronics used in current experiments.

Presented thesis is focused on read-out microelectronics that might be used in future HEP experiments. The goal of this work is design of 12-bit analog-to-digital converter with very low power consumption (in range of single mW) capable to work with 40MHz sampling clock.

The thesis is divided into four chapters. First contains brief overview of High Energy Physics experiments – starting with physics behind them, followed by review of LHC, largest currently running experiment, and a role of electronics in its operations. Here also motivations for this works are presented.

Chapter two reviews basic definitions and parameters (both dynamic and static) connected with ADCs in general, which will be used throughout the thesis. Furthermore most popular ADC architectures are presented and example applications are mentioned.

In third chapter various approaches to successive approximation ADC are reviewed in detail accompanied by results of Matlab simulations of power consumption of each configuration. Based on presented informations the choice of configuration used in this design is justified. In this chapter also general considerations about SAR ADC building blocks are presented.

Fourth chapter presents in detail designed converter – chosen architecture for each block and it's working principles are explained (heavily relying on theories and equations from previous chapter). Here also are presented simulations results of each block separately and ADC as a whole.

Thesis is than concluded with a summary which reviews achieved goals and a brief discussion of potential future work.

# 1 | High Energy Physics experiments

## **1.1** Physics in HEP experiments

The main theory currently used to describe particle physics is Standard Model. It was developed in 1970s by Steven Weinberg, Sheldon Glashow and Abdus Salam and is still applied to explain results of many high energy physics experiments. According to this theory the Universe is built out of structureless particles that can be divided into two groups having 6 members each:

- leptons (having a unity electric charge  $e^-$ ):  $e^-$ ,  $\nu_e$ ,  $\mu^-$ ,  $\nu_\mu$ ,  $\tau^-$ ,  $\nu_\tau$

- -quarks (having fractional electric charge  $\frac{2}{3}e^-$  or  $-\frac{1}{3}e^-$ ): up, down, top, bottom, strange, charm

Interactions in Standard Model are described as exchange of bosons, different for each interaction (photons for electroweak, gluons for strong,  $W^+$ ,  $W^-$ ,  $Z^0$  for weak and not verified experimentally gravitons for gravitational interactions).

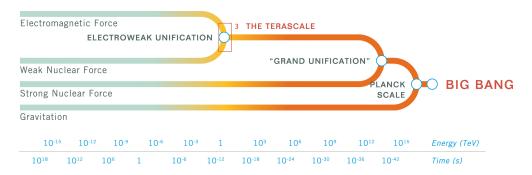

In the years following it's introduction studies of particle physics using Standard Model shown that for energies in range of teraelectronovolts electromagnetic interaction and weak interaction can be in fact described by one mechanism (called electroweak interaction) - this lead to extrapolation of theory, saying that in fact for high enough energy scale all interaction become one, as presented at Figure 1.1. To better describe unification of electromagnetic and weak interactions supersymetric particles were postulated, which were supposed to enable the unification mechanism.

Figure 1.1: Energy scale for unification of fundamental interactions. [1]

Originally Standard Model postulated that all bosons are massless, but experiments UA1 and UA2 carried out in CERN in 1980s proved otherwise. This discovery lead to modification of Standard Model - Higgs mechanism was introduced, explaining inconsistency between theory and experimental data by adding new particle, Higgs boson, which by interaction with other particles gave them mass.

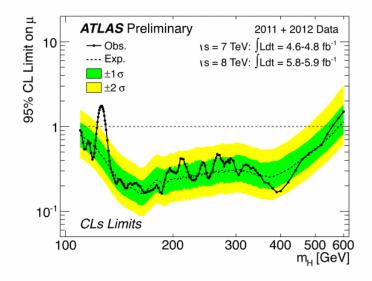

To experimentally verify existence of supersymetric particles and Higgs boson Large Hadron Collider (LHC) was build at CERN - first HEP experiment capable of producing and observing particle interactions at energies in teraelectronovolt range. At  $4^{th}$  July 2012 first results of this experiment were published showing that a particle consistent with characteristics of Higgs boson was observed [2] (Figure 1.2). Despite of this tremendous achievement experiments at LHC are not finished – though new particle was found it's exact characteristics must be further examined to verify if it is indeed a Standard Model Higgs boson or other kind of boson as predicted by theories which go beyond Standard Model [3].

Figure 1.2: Experimental limits from ATLAS on Standard Model Higgs production in the mass range 110-600 GeV. The solid curve reflects the observed experimental limits for the production of a Higgs of each possible mass value (horizontal axis). The region for which the solid curve dips below the horizontal line at the value of 1 is excluded with a 95% confidence level (CL). [2]

Despite this newest discoveries one must remember though, that Standard Model is by no means the final model of particle physics - it presents a very good description of particles as we currently understand them, but it also has its weaknesses:

- it does not incorporate gravitational interactions,

- it requires many additional parameters to be introduced to explain some phenomena (e.g. neutrino oscillations, two independent masses for weak bosons),

- it does not explain some of particle's quantum numbers (e.g. electric charge, colour).

## **1.2** Present and future HEP experiments

As have been mentioned in previous section currently the largest experiment of high energy physics is Large Hadron Collider at CERN. It is situated in 27 km long tunnel, formerly used by Large Electron Positron Collider. LHC is designed to collide two proton beams with maximum energy of 8 TeV in the centre-of-mass or two lead ions beams with energy of 5.5 TeV per nucleon pair. Acceleration of beam to maximal energy is a complicated process consisting of four stages (in case of proton beams) [4]:

- Linac-2 production of proton beam with energy of 50 MeV

- PSB acceleration of beam from Linac-2 to kinetic energy of 1.4 GeV

- PS further acceleration of beams up to 26 GeV

- SPS final injector for LHC (also providing beam for COMPASS and CNGS projects), achieving beam energy of 450 GeV

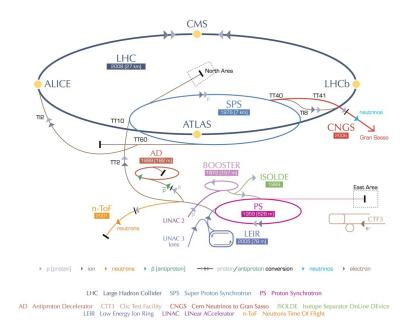

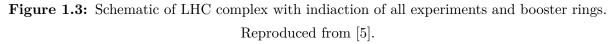

After injection into LHC beam is further accelerated to maximal energy and kept on right track using superconducting magnets. Two proton beams circulate LHC ring in opposite direction inside two separate channels and are intersected only in four places where main experiments are located (schematic view of LHC complex in presented in Figure 1.3):

- ATLAS largest of LHC experiments, general purpose detector (search for Higgs boson, supersymetric particles, dark matter, etc.)

- CMS second largest experiment, also general purpose

- LHCb designed to study asymmetries between B and  $\overline{B}$  mesons

- ALICE build to study properties of strongly interacting matter at extreme energy densities (quark-gluon plasma) during lead ions collisions

It was foreseen that some of the innermost parts of detectors will suffer from performance degradation due to radiation effects after a few years of running the experiment. To remedy this a long-term plan to remove damaged parts and replace them with upgraded substitutes was adopted. This plan assumes a series of upgrades, done in two phases, to end approximately at year 2021, leading to increase in collision energy of proton beams to 14 GeV and ten-fold increase in luminosity (number of events per second) – hence the name of final configuration of the machine is High Luminosity LHC. This will allow to further improve on accuracy of studies (e.g. measure more precisely mass of newly discovered boson) and also extend possibilities in terms of new particles and phenomena discoveries.

Although increase in energy and luminosity in HL LHC will lead to possibility of more precise measurements, there is a fundamental barrier that limits accuracy – both LHC and HL LHC use proton beam. Because protons have their own internal structure (two up quarks and one down quark) their collisions produces high background, which prevents achieving high precision needed to answer questions about Higgs boson mass, spin, parity, etc. A solution is to use structureless particles – leptons, which collisions should be much cleaner and therefore observations and measurements of new particles would be made easier. Since electrons are only stable leptons, they are natural choice in this case, but their low mass (about 2000 times lower than that of a proton) causes them to radiate their energy much more rapidly when their path is curved (bremsstrahlung radiation is proportional to  $m^{-4}$ ). Therefore successors to LHC will be linear colliders and plans together with research & development work for two possible candidates (ILC – International Linear Collider and CLIC – Compact Linear Collider) have been undergoing for past few years – their design specifications can be found in Table 1.1.

| Parameter                                                           | ILC               | $\operatorname{CLIC}_{500GeV}$ | $\operatorname{CLIC}_{3TeV}$ |

|---------------------------------------------------------------------|-------------------|--------------------------------|------------------------------|

| centre-of-mass energy $[GeV]$                                       | 500               | 500                            | 3000                         |

| peak luminosity $\left[\frac{1}{s \cdot cm^2}\right]$               | $2 \cdot 10^{34}$ | $2.3\cdot 10^{34}$             | $5.9\cdot10^{34}$            |

| pulse rate $[Hz]$                                                   | 5                 | 50                             | 50                           |

| number of bunches per pulse                                         | $\sim 3000$       | 354                            | 312                          |

| bunch spacing $[ns]$                                                | 330               | 0.5                            | 0.5                          |

| particles per bunch                                                 | $2 \cdot 10^{10}$ | $6.8\cdot 10^9$                | $3.7\cdot 10^9$              |

| accelerating gradient $\left\lceil \frac{MV}{m} \right\rceil$       | 31.5              | 80                             | 100                          |

| energy loss due to bremsstrahlung $\left[\frac{\Delta E}{E}\right]$ | 0.03              | 0.07                           | 0.28                         |

| total AC power consumption $[MW]$                                   | 230               | 271                            | 582                          |

Table 1.1: Basic design parameter for the ILC and the CLIC accelerators [6].

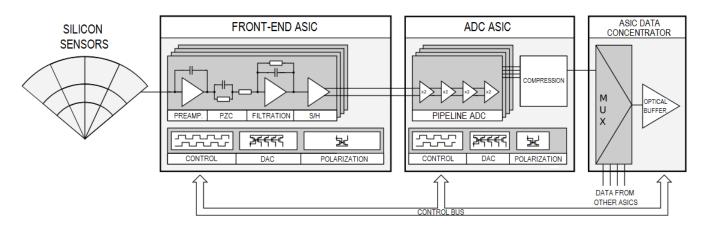

General layouts of both accelerators are similar (therefore only ILC's schematic is presented – Figure 1.4) but their build methodology, final specifications and experimental conditions are very different. Full comparison of the two is far out of scope of this work but two differences will be pointed out:

- centre-of-mass energy while ILC uses 1.3GHz Superconducting RF cavities to accelerate electrons over a course of over 30 km to energy of 500GeV, CLIC is considered to be designed in multi-stage way to achieve energy of 500GeV, 1.5TeV or 3TeV depending on stage. Operation frequency of CLIC is 30GHz, which leads to device length of 37.5km for maximal energy,

- bunch spacing much shorter time between subsequent bunches (0.5ns for CLIC vs. 330ns for ILC) makes a very significant difference for electronics needed for detectors time-tagging combined with good pileup management are essential for CLIC, while in ILC each bunch can be processed separately.

Figure 1.4: Schematic of LHC complex with indiaction of all experiments and booster rings [1].

Choice between two designs will be determined be results from LHC, so in light of recent discovery of new boson ILC seems like a more probable candidate. On the other hand data analysis from ATLAS and CMS suggest that there is no new physics below 1TeV [7], so if LHC will find some signs of supersimetric particles in higher energies proceeding with CLIC will be the only choice.

## **1.3** Read-out electronics

Detectors used in each of experiments described in previous section are very different from one another - they are designed with different specifications (detecting different kinds of particles, working with different collision energies and luminosities, etc.) but all of them require very specific read-out electronics and its design have to take into consideration not only appropriate functionality but also many additional factors:

- effects connected to prolonge exposure to high levels of radiation (increased leakage current, shifts in transistor's threshold voltages, signle event upsets, etc.)

- very high number of read-out channels combined with small avaiable space

- need to minimize amount of used materials (to reduce secondary interactions with beam collision products)

- high relaiability (due to as compact construction of detectors as possible and presence of high energy particle beams, all repairs and replacements of parts are problematic)

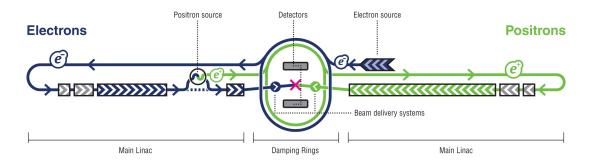

All those factors make it necessary to design read-out electronics as Application Specific Integrated Circuits (ASIC) instead of using complex systems of discrete elements. As example of such ASIC system a read-out chain for LumiCal detector (part of detector for ILC) is presented on Figure 1.5.

Figure 1.5: LumiCal's readout electronics flow chart. Reproduced from [10].

LumiCal is a sandwich calorimeter (it is build out of staggered layers of tungsten absorber and silicon sensors). When an electron or positron pass through such structure they deposit an electric charge in sensor layer and pass through it, but when they encounter tungsten they quickly lose their momentum resulting in bremsstrahlung radiation. This causes (in environment of heavy tungsten nuclei) creation of new electron - positron pairs – so called electromagnetic shower occurs. Shape of this shower and number of penetrated layers is determined mainly by kind of particle which passes through and its energy. Role of read-out electronics is to measure the charge collected by each sensor and pass it to Data Acquisition system (DAQ). Front-end ASIC is supposed to extract information from silicon sensor, shape and amplify it and store the information in sample & hold device. Because of ease of transmition and data processing signal from front-end is converted to digital form using an analog-to-digital converter. Output stage – data concentrator – passes informations from ADC to DAQ via optical buffer.

### **1.4** Motivations for this work

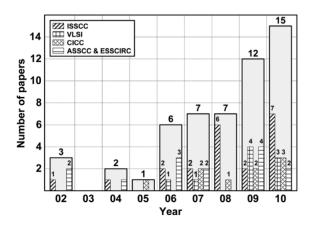

As was mentioned in previous sections future HEP experiments will require more precise measurement electronics than used presently. This thesis is a research & development work investigating if ADC with parameters of potential interest to future experiments (low power, 12-bit resolution with 40MHz sampling frequency, 144  $\mu m$  pitch) is feasible to design using 130nm technology. Inspiration for this attempt is very high activity related to SAR ADC resulting in quite rapid development of new variations and improvements for this architecture – this trend can be seen in number of publications on this topic in recent years (as presented in Figure 1.6). Focus will be especially given to new method of capacitive DAC switching which lead to very significant reduction in power consumption.

Figure 1.6: Number of articles about SAR ADC published in recent years. [8]

# 2 Overview of analog-to-digital converters

### 2.1 Basic definitions

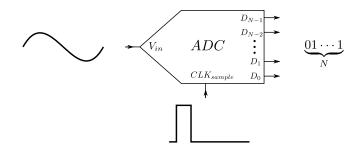

An analog-to-digital converter is a device connecting analog and digital signal domains - it translates an analog signal (continuous in time and amplitude) into a digital word (composed of few signals with binary quantised amplitudes denoted 0 for  $V_{ref,min}$  and 1 for  $V_{ref,max}$  – see figure 2.1).

Figure 2.1: Schematic representation of operation of ADC.

Due to the very nature of this process translation will never be ideal – for two input samples ADC's output will be different only if the samples differ by more than minimal voltage recognizable by ADC. This minimal value is called *Least Significant Bit (LSB)* and for *N*-bit converter is defined as [9]:

$$LSB \equiv \frac{V_{ref}}{2^N} \tag{2.1}$$

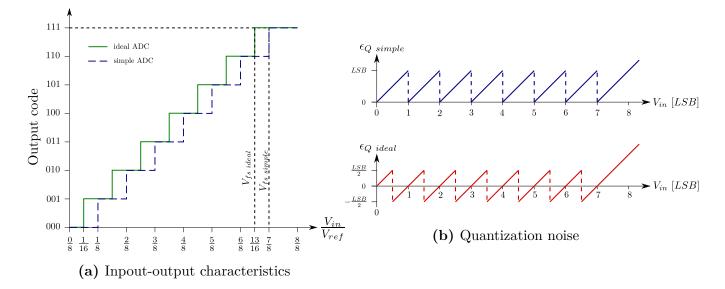

This inaccuracy results in multi-step input-output characteristic (example shown in Figure 2.2a) and introduces so called quantization noise – difference  $\epsilon_Q$  between real value of input and its quantized substitute (presented in Figure 2.2b). Figure 2.2 contains plots for two examples of ADC – "simple ADC" which functions exactly as described in previous paragraph (change of input voltage by 1 *LSB* results in change of output code by one) but, as can be observed by comparing equations 2.19 and 2.20, exhibits lower signal-to-noise ratio than "ideal ADC" (same characteristics as simple one but with added offset  $V_{offset} = \frac{1}{2}LSB$ ). This claim

is proven in section 2.1.2.

Figure 2.2: Consequences of input signal quantization shown for 3-bit ADC.

Output of ADC can be therefore expressed as (assuming binary-weighted output bits):

$$V_{out} = V_{ref} \cdot \sum_{i=0}^{N-1} D_i 2^i$$

(2.2)

where  $D_i$  represents value of *i*-th digital output.

On figure 2.2a two characteristic voltage levels can be noticed:  $V_{ref}$  – reference voltage and  $V_{fs}$  – full scale voltage. They are connected through relation:

$$V_{fs,simple} = V_{ref} - 1 \cdot LSB \tag{2.3}$$

$$V_{fs,ideal} = V_{ref} - \frac{3}{2} \cdot LSB \tag{2.4}$$

Combining equations 2.1 and 2.3 leads to other, also commonly used, definition of LSB:

$$LSB = \frac{V_{fs}}{2^N - 1} \tag{2.5}$$

#### 2.1.1 Static parameters

There are many characteristics that can be used to measure how much given ADC differs from an ideal one. In this section those used when sampling static or slowly changing signals will be introduced.

#### Offset error

As mentioned in previous section an ideal ADC has an offset of  $\frac{1}{2}LSB$  – any deviation from this value is considered an offset error (also known as zero-scale error). To put this in other words – difference between  $\frac{1}{2}LSB$  and voltage causing first ADC transition is an offset voltage. Origins of this error can be different for different architectures (offset in comparators in flash ADC, offset in DAC for SAR, etc.) but in general it is correlated with mismatch of components of an ADC or changes in reference voltages.

#### Gain error

Gain error, also called slope factor error, is a difference in slope of straight line drawn through the transfer characteristics and the slope of corresponding line of an ideal ADC.

#### Full scale error

Full scale error is in principle very similar to offset error – it is difference between ideal value of full-scale voltage ( $V_{fs} = V_{ref} - \frac{3}{2}LSB$ ) and measured one that triggers transition to last output code available. This error is a result of both offset error and gain error.

#### Differential NonLinearity (DNL)

While three kinds of errors mentioned above are not very severe since they can be removed with measurement calibration, DNL and described next INL are more important.

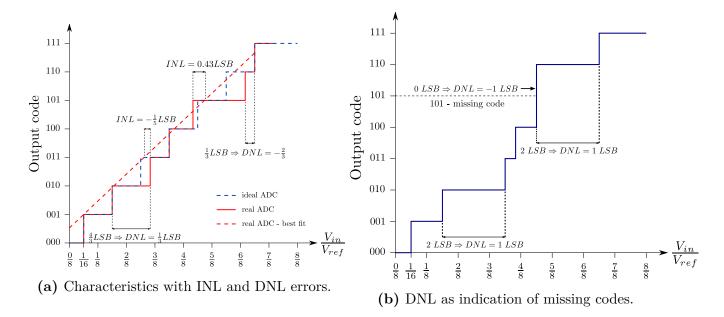

For an ideal ADC difference in input voltage for which output code change  $\Delta V_{in\ change}$  is, by definition, equal to 1 *LSB*. For real ADC value of  $\Delta V_{in\ change}$  will most likely differ for each output code due to elements mismatch, process variation, etc. Differential nonlinearity is a measure of how much  $\Delta V_{in\ change}$  changes from code to code and can be defined as [11, 12] (example of transfer curve of an ADC exhibiting DNL errors is presented in Figure 2.3a):

$$DNL(m) = \frac{\Delta V_{in\ change}(m) - LSB}{LSB} = \frac{V_{in}(m) - V_{in}(m-1) - LSB}{LSB}$$

(2.6)

$$[DNL(m)] = LSB$$

Value of DNL provides also information about missing codes [12] (ass can be observed in Figure 2.3b):

$-DNL(m) \leq -1 LSB \Rightarrow m$ -th code will be missing

−  $DNL(m) \ge 1$   $LSB \Rightarrow m$ -th code is present, (m+1)-th presence depends upon (m+2)-th transition value

Figure 2.3: Example of INL and DNL errors for 3-bit ADC.

#### Integral nonlinearity (INL)

Information about converters linearity is obtained by calculating INL [11, 12]:

$$INL(m) = \frac{V_{meas}(m) - V_{fit}(m)}{LSB}$$

$$[INL(m)] = LSB$$

(2.7)

where  $V_{meas}(m)$  is measured value of *m*-th transition step and  $V_{fit}(m)$  is value of this level calculated from straight line fit to transfer function (as presented in Figure 2.3a). In literature two ways of fitting are reported:

- fit only through first and last point of transfer characteristics

- use best fit to fit all point from characteristics (used in this work)

Integral non-linearity measures monotonicity of converter – if highest value of INL is below  $\frac{1}{2}LSB$  converter is monotonic [11]. One of the most important characteristics of an ADC is its *Effective Number Of Bits (ENOB)*, which informs about realistic resolution of converter during normal operation. It can be calculated using INL as [13]:

$$ENOB = \log_2\left(\frac{2^N}{\sqrt{1 + \frac{12}{2^N - 2} \cdot \sum_{m=1}^{2^N - 2} INL(m)^2}}\right)$$

(2.8)

#### 2.1.2 Dynamic parameters

Dynamic parameters inform about converter's behaviour when sampling fast changing signals. This shows influence of noise, sampling time uncertainty, nonlinear distortions, etc. Results obtained through dynamic parameters depend not only on ADC itself, but also on signals used as input (amplitude, frequency) and sampling clock (frequency, jitter). This makes dynamic parameters measurement more demanding than static ones.

One of commonly used method of measurement is through analysis of discrete Fourier transform (DFT) of converters response to input sinus signal with amplitude  $\frac{V_{ref}}{2}$ . DFT transforms discrete K-element sequence of samples from time domain x(k) into its equivalent in frequency domain X(m):

$$X(m) = \sum_{k=0}^{K-1} x(k) e^{-\frac{j2\pi km}{K}}$$

(2.9)

Result of this transformation is a periodic K-element sequence of values X(m) distributed evenly along frequency axis at points:

$$f(m) = m \cdot \frac{f_{sample}}{K} \tag{2.10}$$

where  $f_{sample}$  is sampling frequency of x(k). Obtaining correct results depends upon choosing proper input signal frequency  $f_{in}$  – it should be related to sampling frequency  $f_{sample}$  and number of collected samples K by relation [10, 16]:

$$f_{in} = \frac{J}{K} f_{sample} \tag{2.11}$$

where J is mutually prime number to K. If this condition is not met, spectral leakage will occur – input signal will be spread among whole frequency range f(m) instead of one point, which will lead to false results of DFT.

Fourier transform can be used to analyse signals constituted of many components (e.g. signal and its harmonic) thanks to its linearity – transform of sum of signals is equivalent to sum of transformed signals [15]:

$$X_{sum}(m) = \sum_{k=0}^{K-1} \left[ x_1(k) + x_2(k) \right] e^{-\frac{j2\pi km}{K}} = \sum_{k=0}^{K-1} x_1(k) e^{-\frac{j2\pi km}{K}} + \sum_{k=0}^{K-1} x_2(k) e^{-\frac{j2\pi km}{K}} = X_1(m) + X_2(m)$$

(2.12)

#### Total Harmonic Distortion (THD)

Harmonics distortions at ADCs output (presence of harmonics of input signal) appear due nonlinearities in converter and due to missing codes. To measure how much those distortions degrade ADC performance parameter THD was defined as ratio of total power of harmonics to power of fundamental signal [10, 16]:

$$THD = 20 \log_{10} \left( \sqrt{\frac{\sum_{k=2}^{K_H+1} X_{avrg}^2((k \cdot f_{sig}) \mod f_{sample})}{X_{avrg}^2(f_{sig})}} \right)$$

(2.13)

$$[THD] = dB$$

where  $K_H$  is number of harmonics taken into account (usually  $K_H = 10$ ) and  $X_{avrg}(i)$  is average of measured values of frequency interval f(i).

#### Signal to Non-Harmonic Distortion (SNHR)

To measure influence of error sources other than harmonics, e.g. quantization noise and noise introduced by capacitances and resistances, SNHR is used. It is defined as power of signal to total power of all other frequency intervals within measured bandwidth, excluding harmonics frequencies [10, 16]:

$$SNHR = 20 \log 10 \left( \sqrt{\frac{X_{avrg}^2(f_{sig})}{\sum_{k=1}^{2^{K}-1, \ i \neq f_{h[k]}} X_{avrg}^2(f(i))}} \right)$$

(2.14)

[SNHR] = dB

where  $f_{h[k]} = (k \cdot f_{sig}) \mod f_{sample}$ .

#### Signal to Noise and Distortion (SINAD)

Dynamic parameter which describes overall performance of ADC is SINAD – here both harmonic and nonharmonic sources of noise are taken into account. SINAD is defined as ratio of power of signal to total power of noise and distortion within measured bandwidth:

$$SINAD = 20 \log 10 \left( \sqrt{\frac{X_{avrg}^2(f_{sig})}{\sum_{k=1}^{2^K - 1, \ i \neq f_{sig}} X_{avrg}^2(f(i))}} \right)$$

(2.15)

$$SINAD] = dB$$

#### Effective Number Of Bits (ENOB)

This parameter was already defined in section 2.1.1 among static parameters, but it can be calculated also based on dynamic parameters. Equation for ENOB is based on definition of Singal to Noise Ratio (SNR) for ideal ADC. SNR is defined as [14, 16]:

$$SNR = \log_{10} \left( \frac{Power \ of \ signal}{Power \ of \ noise} \right)$$

$$[SNR] = dB$$

(2.16)

Standard input signal is a sinus wave with amplitude of  $\frac{V_{ref}}{2}$ , thus its average power  $\langle P_{sin} \rangle$  can be calculated as (using very common simplification  $R = 1\Omega \Rightarrow P = \frac{V^2}{R} = V^2$ ):

$$\langle P_{sin} \rangle = \frac{1}{T} \int_0^T \left( \frac{V_{ref}}{2} \sin(2\pi ft) \right)^2 \mathrm{d}t = \frac{V_{ref}^2}{8}$$

(2.17)

To calculate noise power we assume that all components are ideal, so only quantization noise is present (this assumption poses some restrictions on quantization process – quantization levels must be uniform, equiprobable, not correlated to input and large number of them must exist [14]; all those conditions are met for an ideal 12-bit ADC with high swing input signal). From Figure 2.2b for ideal ADC it is clear that  $\epsilon_Q \in \left[-\frac{LSB}{2}; \frac{LSB}{2}\right]$ , and additionally we assume that probability distribution of quantization error  $P(\epsilon_Q)$  is constant within mentioned range and equal to zero outside it. Probability normalization leads to:  $\int_{-\infty}^{\infty} P(\epsilon_Q) d\epsilon_Q = 1 \Rightarrow P(\epsilon_Q) = \frac{1}{LSB}$ . All this allows to calculate the average noise power as:

$$\langle P_{noise} \rangle = \int_{-\infty}^{\infty} P(\epsilon_Q) \epsilon_Q^2 d\epsilon_Q = \frac{1}{LSB} \int_{-\frac{LSB}{2}}^{\frac{LSB}{2}} \epsilon_Q^2 d\epsilon_Q = \frac{LSB^2}{12}$$

(2.18)

Combining equations 2.1, 2.16, 2.17 and 2.18 results in:

$$SNR_{ideal \ ADC} = 10 \log_{10} \left(\frac{3}{2} \cdot 2^N\right) \approx 6,02 \cdot N + 1,76 \ [dB]$$

(2.19)

Expression 2.19 shows highest achievable SNR for N-bit converter. For comparison – if an ADC would have a transfer characteristics like "simple ADC" from figure 2.2a than its noise power would be  $\langle P_{noise\ simple} \rangle = \frac{1}{LSB} \int_0^{LSB} \epsilon_Q^2 d\epsilon_Q = \frac{LSB^2}{3}$ , hence

$$SNR_{simple\ ADC} = 10\log_{10}\left(\frac{3}{8} \cdot 2^{N}\right) \approx 6,02 \cdot N - 4,26\ [dB]$$

(2.20)

Calculating value of N from equation 2.19:

$$N = \frac{SNR - 1.76}{6.02} \tag{2.21}$$

By substituting ENOB for N and SINAD for SNR commonly used equation for ENOB is obtained [16]:

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

(2.22)

## 2.2 Overview of ADC architectures

One of most important theorems in signal conversion is Nyquist-Shannon theorem [14]:

A band limited signal x(t), which Fourier spectrum  $X(j\omega)$  vanishes for frequencies  $|f| < \frac{1}{2} f_{sample}$  is fully described by a uniform sampling  $x(\frac{n}{f_{sample}})$ , where  $n \in \mathbb{N}$ .

Based on this theorem all existing architectures of analog-to-digital converters can be divided into two categories:

- Nyquist rate ADC input signals have maximal frequency twice (or little bit more) lower than that of sampling. This category is represented by many different architectures, some of which are:

- Flash converter

- Pipeline converter

- Successive approximation converter

- oversampling ADC frequency of sampling is many times higher than that of input signals. Only  $\Sigma \Delta$  converters works in this way.

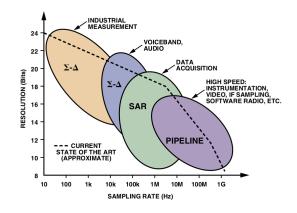

Each architecture is suitable for different purpose depending on number of bits, sampling frequency, power and area consumption needed (as presented in Figure 2.4). Following section will give a brief summary of each mentioned architecture.

Figure 2.4: General allotment of different architectures of ADC. [17]

## 2.2.1 Oversampling ADC

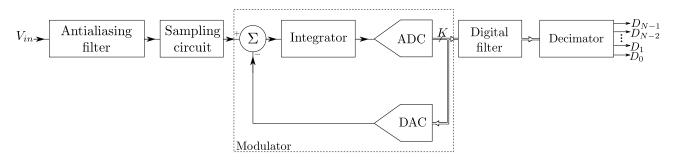

Oversampling ADCs work very differently compared to Nyquist rate converters – they relay on noise shaping and oversampling followed by averaging of input signal. They are capable of achieving very high resolution (even 24-bits) but maximal input signal frequency rarely exceeds few MHz. For those reasons they are mostly used for processing of sound. Operations of  $\Sigma - \Delta$ converter (only kind of oversampling ADC) is easiest to summarize by explaining function of each of its building blocks (block diagram of converter is shown in Figure 2.5):

- Antialiasing filter filters out any noise outside signal bandwidth, so it will not be aliased back close to signal during oversampling

- Sampling circuit samples input signal with frequency many times higher than frequency resulting from Nyquist-Shannon theorem

- Modulator many different kinds of modulators are used varying mainly in number of incorporated integrators and resolutions of analog-to-digital and digital-to-analog converters (not necessarily having the same resolution), but simplest one can for example consist of one integrator, comparator as ADC and switch as DAC connected in one feedback loop. This block has two main functions:

- $\circ\,$  shaping noise in such a way that majority of it is shifted to high frequencies

- producing at the output a digital signal with frequency equal to sampling frequency and mean value equal to value of sampled input

- Digital filter most commonly a low-pass filter, which should remove noise shifted to high frequencies

- Decimator produces a lower frequency (compared to sampling frequency) converter output signal by averaging filtered modulator output over set period of time. Simplest implementation is a counter which counts number of pulses over pre-set number of cycles.

**Figure 2.5:** Block diagram of  $\Sigma - \Delta$  ADC.

#### 2.2.2 Nyquist rate ADC

#### Flash converter

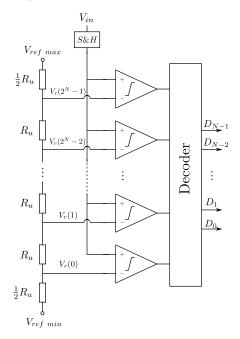

Principle of operation of flash ADC is simple – input voltage is compared with every transition point of ADC at the same time, resulting in information on how many LSBs are required to match sampled voltage level. This number is than translated into binary value by digital logic – thanks to such means of operation flash ADC is fastest of all ADC.

Figure 2.6: Schematic of simple Flash ADC.

Simple implementation using resistive divider is shown at Figure 2.6. First and last resistor have half of unit resistance value  $R_u$  to achieve transfer characteristic similar to ideal ADC from Figure 2.2a. In such configuration one of the inputs of each comparator is  $V_{in}$  and second one is  $V_r(i)$ :

$$V_r(i) = \frac{i + \frac{1}{2}}{2^N - 1} \left( V_{ref \ max} - V_{ref \ min} \right) + V_{ref \ min}$$

(2.23)

The way this converter works limits its usage to relatively low resolutions due to various reasons:

- rise in resolution by 1 bit requires twice more transition points hence twice smaller resistances in divider scaling those down to very small values introduces very strong influence of mismatch and because of that becomes impossible for high resolution

- number of required comparators is  $2^N 1$ , resulting in exponential growth of power consumption and area of converter

- offset of all comparators needs to be kept below  $\frac{1}{2}$  LSB, resulting in very small and hard to achieve values for high resolutions

#### Pipeline converter

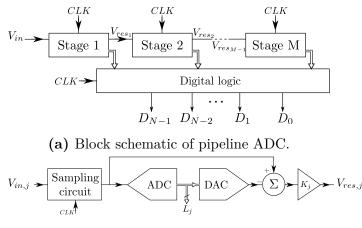

Pipeline converter is build out of cascade of individual stages (not necessarily identical) each performing part of conversion (simple block diagram of pipeline ADC is presented in Figure 2.7).

(b) One of stages in pipeline converter.

Figure 2.7: Pipeline architecture.

Pipeline ADC's sequence of conversion starts with input signal being sampled by 1<sup>st</sup> stage (as shown in Figure 2.7b). This sample is converted to digital value by an *L*-bit ADC (*L* can have any value, but most commonly low values are used, often single bit). This value serves as one output of stage – conversion result. ADCs output is than converted back to analog form, subtracted from original input and the result is amplified  $K_1$  times producing residual value  $V_{res_1} = (V_{in} - V_{DAC_1}) \cdot K_1$ , or put in more general form for *j*-th stage;:

$$V_{res,j} = (V_{res,j-1} - V_{DAC,j}) \cdot K_j \tag{2.24}$$

The residual value  $V_{res,j}$  serves as input for next stage. Gain factor  $K_j$  is often set to be  $2^{L_j}$  so all stages can use the same reference voltage. Output of each stage is passed to digital logic, which after last stage finishes conversion forms digital output word based on results of stages conversions. For converter build out of M stages it takes M + 1 clock cycles to convert signal (assuming that digital logic operation takes only one cycle), but advantage of this architecture is that after given stage has done conversion for one sample it can immediately start conversion for another one – in such mode of operation after initial wait of M + 1 clock cycles conversion results are provided every clock cycle (with the same resolution) despite the fact that conversion itself always takes M + 1 cycles. Pipeline ADC achieve medium resolution (8 to 12 bits) and consume moderate amounts of power – for those reasons they were very commonly used but in recent years are being superseded by SAR ADC.

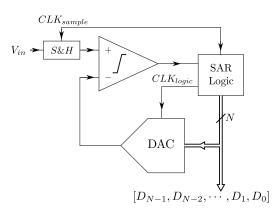

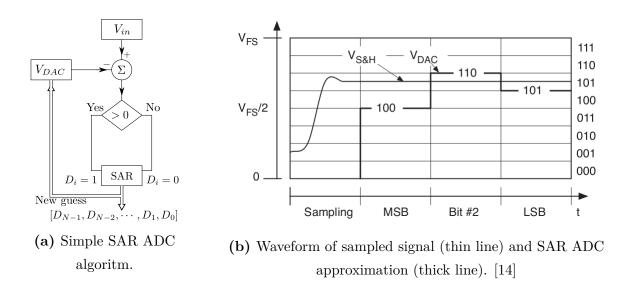

#### Succesive Approximation Register (SAR) converter

Schematic of simple SAR ADC is shown on Figure 2.8. It consists of sample and hold circuit, comparator, SAR control logic and DAC (used to produce reference voltage for comparator). Conversion starts by sampling input signal (sampling duration is controled by  $CLK_{sample}$ ) at the end of which the logic set Most Significant Bit (MSB) to 1 causing DAC's output voltage  $V_{DAC}$  to rise to  $\frac{1}{2}V_{ref}$ . Than comparator decides which of those two voltages is higher:

- if  $V_{in} > V_{DAC}$  than the value of sampled voltage is higher than  $\frac{1}{2}V_{ref}$ , so first bit of output word was guessed corectly and remains 1

- if  $V_{in} < V_{DAC}$  than the value of sampled voltage is lower than  $\frac{1}{2}V_{ref}$ , so first bit of output word was guessed incorectly and is reset to 0

After this check next bit (MSB-1) is changed to 1 (resulting in  $V_{DAC} = \frac{3}{4}V_{ref}$  if MSB = 1 or  $V_{DAC} = \frac{1}{4}V_{ref}$  if MSB = 0) and whole process is repeted until all N bits are resolved – this algorithm can be summarized as shown on Figure 2.9a and example waveform is shown on Figure 2.9b.

Figure 2.8: Block schematic of simple SAR ADC.

Although this way of approximation works correctly it is quite wasteful in regard of power e.g. if  $V_{in} = V_{ref\ min}$  DAC is charged and discharged for every bit wasting energy. For this reason SAR architecture was not very popular until few years ago when improved implementations of successive approximation algorithm were proposed – those, alongside with more detailed examination of SAR ADC will be described in the next chapter.

# 3 | SAR ADC – algorithm variants and building blocks general considerations

## 3.1 Variants of successive approximation algorithm

As was mentioned in previous chapter recent years brought many developments in successive approximation ADCs. This evolution of SAR architecture is mainly driven by need for medium resolution ultra low-power ADCs and is made possible by advances of technology used to manufacture integrated circuits and optimization of SAR ADC architecture.

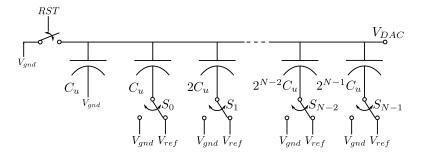

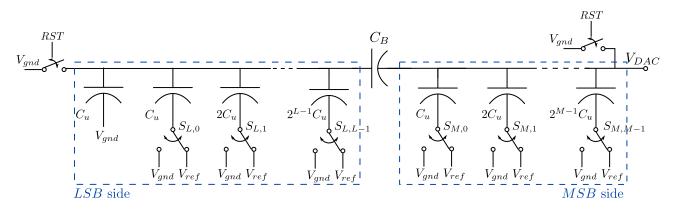

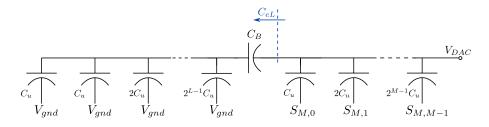

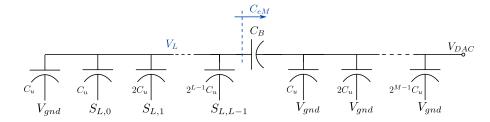

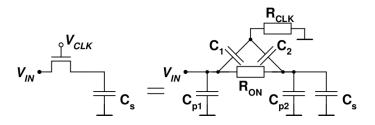

Despite the fact that from the point of view of basic functionality (providing voltage reference) any DAC architecture can be used in SAR ADC (resistor string, R-2R ladder, current steering, etc.) most commonly used one is charge scaling DAC – all reviewed in this chapter successive approximation methods use this kind of digital-to-analog converter. In its simplest implementation (presented in Figure 3.1) it consists of a parallel array of binary-weighted capacitors, resulting in total capacitance  $C_{tot}$  of:

$$C_{tot} = \left(\sum_{i=0}^{N-1} 2^i + 1\right) C_u = 2^N C_u \tag{3.1}$$

where  $C_u$  is unit capacitance. All capacitors are connected together by one plate while second plate of each capacitor is connected to a separate switch  $S_i$  providing a voltage level appropriate at the current conversion phase (in example shown in Figure 3.1 those are: reference voltage  $V_{ref}$  and ground level  $V_{gnd}$ ). Output of such converter  $V_{DAC}$  is a result of voltage division among capacitors.

$$V_{DAC} = V_{ref} \cdot \sum_{i=0}^{N-1} S_i 2^{i-N} + V_{gnd}$$

(3.2)

The main differences between presented methods of successive approximation are architec-

Figure 3.1: Schematic of simple charge scaling DAC.

ture of used DAC and algorithm of its switching, but no matter how an array of capacitors will be modified, the output value will always be a result of voltage division among capacitors. This short overview of charge scaling DAC should have provided enough information to allow understanding of concepts described in this chapter, a more detailed examination of this building block will be presented in chapter 3.2.

Following sections contain overview of some of the more popular variants of SAR algorithm, each illustrated with an example showing all possible states in all conversion stages for 3-bit ADC (except for improved switchback algorithm, were minimal example showing all techniques requires 4-bits). Values of energy marked in all those examples are values drawn from voltage source due to the operation of DAC and are noted over blue arrows showing transitions between stages. In all cases those values are calculated based on the change of the charge stored in capacitors connected to voltage source after switching is done. Assuming that transition between stages starts at  $T_1$  and ends at  $T_2$  the energy drawn from source  $E_{T_1 \to T_2}$  can be calculated as [18]:

$$E_{T_1 \to T_2} = \int_{T_1}^{T_2} i_{source}(t) v_{source}(t) dt = \left\| \begin{array}{c} v(t) = V_{source} \\ i_{source}(t) = \frac{\mathrm{d}Q}{\mathrm{d}t} \end{array} \right\| = V_{source} \int_{T_1}^{T_2} \frac{\mathrm{d}Q}{\mathrm{d}t} dt = V_{source} \int_{Q(T_1)}^{Q(T_2)} \mathrm{d}Q$$

$$(3.3)$$

By definition charge Q stored in capacitor is equal to product of its capacitance  $C_{cap}$  and voltage across it  $V_{cap}$ , leading to:

$$E_{T_1 \to T_2} = C_{cap} V_{source} \left[ V_{cap}(T_2) - V_{cap}(T_1) \right]$$

(3.4)

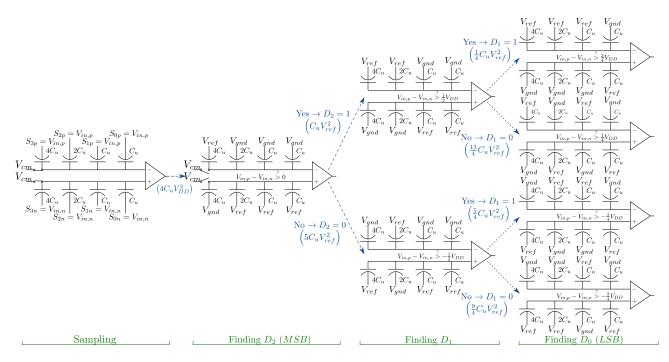

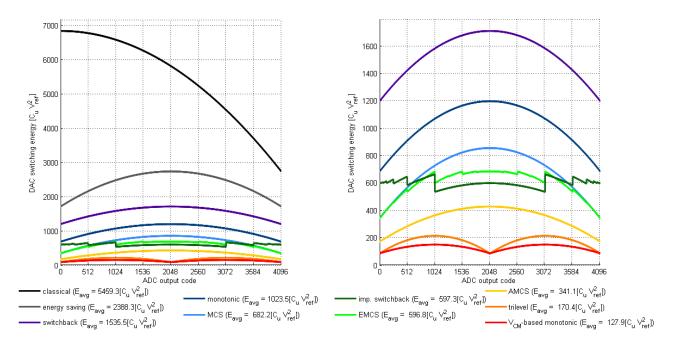

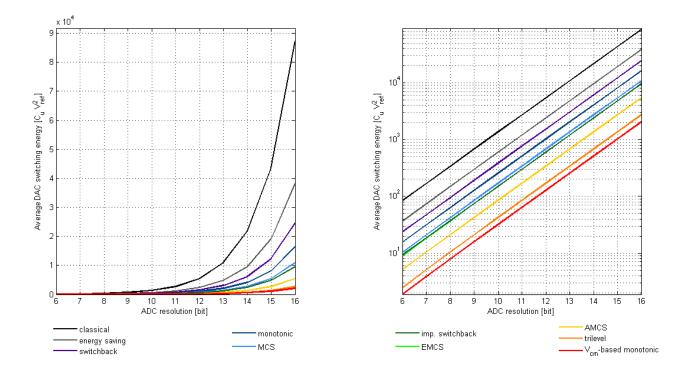

Since the design presented in this work is fully differential all reviewed methods will be also shown in differential configuration. Based on equation 3.4 calculations of energy consumption for all described algorithms were implemented in Matlab 2009b and results are presented throughout this chapter as energy consumption plots. Code itself is included as appendix C.

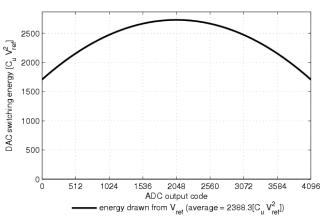

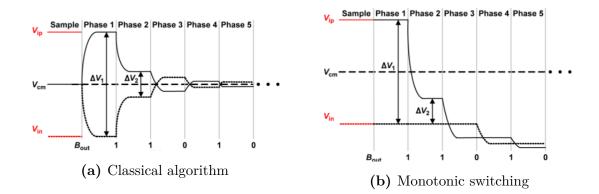

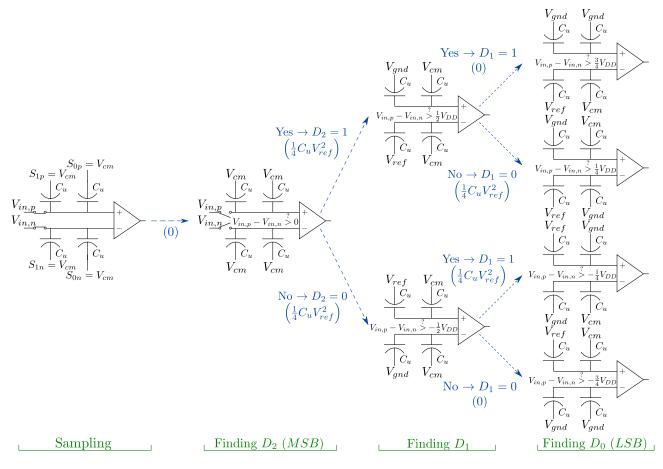

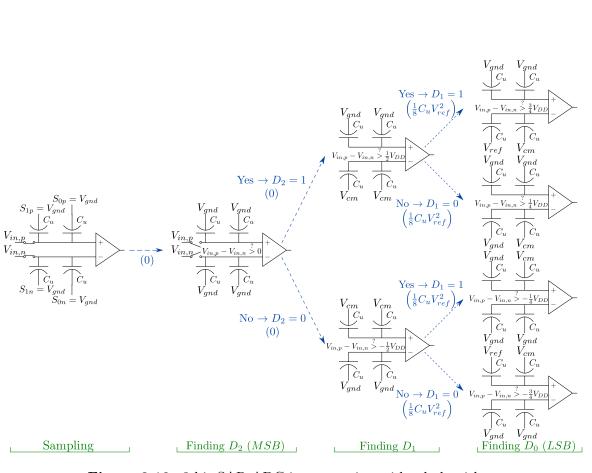

#### 3.1.1 Classical algorithm

In the classical approach [18, 19] (presented in Figure 3.2) two capacitive DACs work in complementary way to converge DAC top plate voltages after sampling to  $V_{cm} = \frac{V_{ref}+V_{gnd}}{2}$ . In sampling phase input is sampled on bottom plate of capacitive DACs while top plates are being charged to common-mode voltage  $V_{cm}$ . When the sampling ends the top plates are disconnected from  $V_{cm}$  and all bottom plates of DAC capacitive network sampling  $V_{in,p}$  are connected to  $V_{gnd}$ , except for biggest capacitor  $2^{N-1}C_u$  which is switched to  $V_{ref}$  (voltage at comparator input for this side is then  $V_{cm} - V_{in,p} + \frac{1}{2}V_{ref}$ ). Bottom plates of DAC network sampling  $V_{in,n}$  are switched in a complementary way  $-2^{N-1}C_u$  is connected to  $V_{gnd}$ , while the rest is switched to  $V_{ref}$ . Then the first comparison is performed  $-D_{N-1}$  which is the Most Significant Bit (MSB) is decided and based on that decision bottom plate voltages of MSB capacitors  $(2^{N-1}C_u)$  are set:

- $D_{N-1} = 1$  if  $V_{in,p} > V_{in,n}$ , resulting in  $S_{N,p} \rightarrow V_{ref}$  and  $S_{N,n} \rightarrow V_{gnd}$

- $D_{N-1} = 0$  if  $V_{in,p} < V_{in,n}$ , resulting in  $S_{N,p} \rightarrow V_{gnd}$  and  $S_{N,n} \rightarrow V_{ref}$

After that the second largest capacitors bottom plates are switched (on  $V_{in,p}$  sampling side to  $V_{ref}$ , on  $V_{in,n}$  sampling side to  $V_{gnd}$ ) and the whole process is repeated. Conversion ends when all bits have been resolved. Every bit found brings the difference between two DACs top plate voltages  $\Delta V_{DAC}$  closer to  $V_{cm}$  – after the last bit is found this difference should be  $|\Delta V_{DAC}| \leq LSB$ .

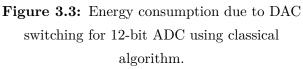

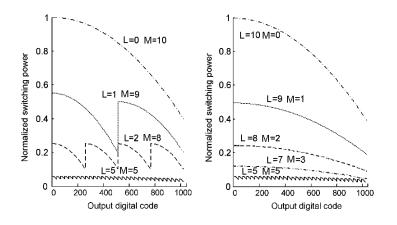

Although this approach to successive approximation is quite intuitive it is also wasteful in respect to power consumption, especially when wrong assumptions are made – this can be seen from Figure 3.3 (energy used for DAC switching for output code  $0(00\cdots00)$  is much higher than for  $4095(11\cdots11)$ ). Overview of most important features of this algorithm is presented in Table 3.1.

Figure 3.2: 3-bit SAR ADC incorporating classical algorithm.

Calculations leading to energy values shown on Figure 3.2 are presented in appendix A. For all other algorithms such calculations can be carried out in the same manner – for this reasons full calculations will be omitted and only results will be presented.

Table 3.1: Features of classical algorithm.

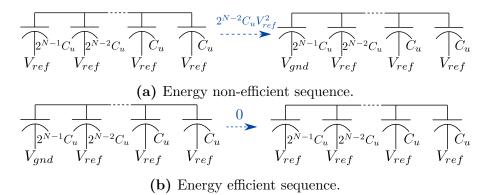

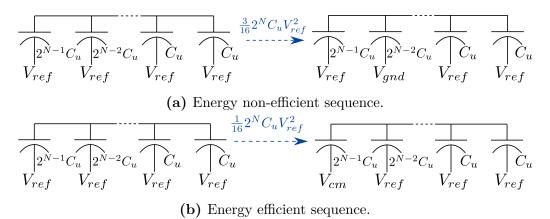

#### 3.1.2 Energy saving

Energy saving algorithm [20] uses modified DAC architecture – second biggest capacitor is split into binary divided array in which each of scaled capacitors can be switched separately. Such configuration allows to share part of charge accumulated in this sub-DAC instead of just discharging  $2^{N-2}C_u$  to ground as happens in classical algorithm. Operations of positive and negative DACs are complementary, so for simplicity only positive DAC switching will be described.

Energy saving algorithm (example of 3-bit ADC using this method is presented in Figure 3.5) implements bottom plate sampling (top plates are held at  $V_{ref}$ ). After sampling is done, top-plates are disconnected from  $V_{ref}$  and all bottom plates are switched to  $V_{gnd}$ . In such state first comparison is made, resulting in finding value of  $D_{N-1}$  and next configuration of DAC's bottom-plate voltages:

-  $D_{N-1} = 1$  if  $V_{in,p} > V_{in,n}$ , leading to  $\forall_i S_{N-2,i,p} \rightarrow V_{gnd}$  and  $\forall_{j \neq N-2} S_{j,p} \rightarrow V_{ref}$

-  $D_{N-1} = 0$  if  $V_{in,p} < V_{in,n}$ , leading to  $\forall_i S_{N-2,i,p} \rightarrow V_{ref}$  and  $\forall_{j \neq N-2} S_{j,p} \rightarrow V_{gnd}$

If  $D_{N-1} = 0$  than *i*-th decision that is 1 will result in connecting capacitance  $2^{N-2-i}C_u$  of sub-DAC to  $V_{ref}$  and  $D_{N-1-i} = 0$  will lead to disconnecting  $2^{N-2-i}$  capacitance from main DAC from  $V_{ref}$  and connecting it to  $V_{gnd}$ . If  $D_{N-1}$  was 1 than operations will be complementary. Figure 3.5 presents an example of 3-bit ADC using this algorithm.

Although this algorithm is more energy efficient than classical one (by 56.25% as can be seen from Table 3.2 or by comparing Figures 3.3 and 3.4), splitting second largest capacitor in separate binary weighted array to be used during switching requires nearly double the number of switches in circuit – for high resolution ADC those switches and buffers needed to drive them might be quite big, resulting in additional area needed for layout.

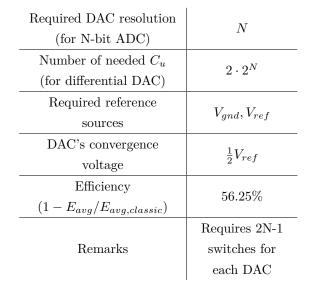

Table 3.2: Features of energy saving algorithm.

Figure 3.4: Energy consumption due to DAC switching for 12-bit ADC using energy saving algorithm.

Figure 3.5: 3-bit SAR ADC incorporating energy saving switching algorithm.

#### 3.1.3 Monotonic switching

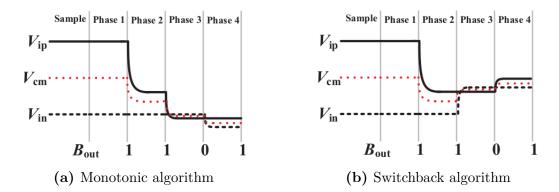

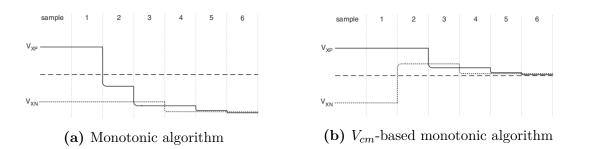

Other name used for this method is set-and-down algorithm [19, 21], idea behind it is to converge voltages sampled on DACs' top plates to  $V_{gnd}$  instead of converging them to  $V_{cm}$ as in classical method - the comparison of  $V_{DAC}$  voltages during conversion for classical and monotonic switching algorithms is presented in Figure 3.6.

During the sampling phase bottom plates of all capacitors are switched to  $V_{ref}$  while input is sampled onto top plates. After sampling is finished top plates are disconnected from input signal, bottom plates remain at  $V_{ref}$  and first comparison is performed. Based on decision of comparator  $D_{N-1}$  is resolved and appropriate bottom plate voltage is changed:

-  $D_{N-1} = 1$  if  $V_{in,p} > V_{in,n}$ , resulting in  $S_{N-2,p} \rightarrow V_{gnd}$  and  $S_{N-2,n} \rightarrow V_{ref}$

-  $D_{N-1} = 0$  if  $V_{in,p} < V_{in,n}$ , resulting in  $S_{N-2,p} \rightarrow V_{ref}$  and  $S_{N-2,n} \rightarrow V_{gnd}$

After that the procedure is repeated until whole digital output word is found (Figure 3.8 shows an example of 3-bit ADC using monotonic switching).

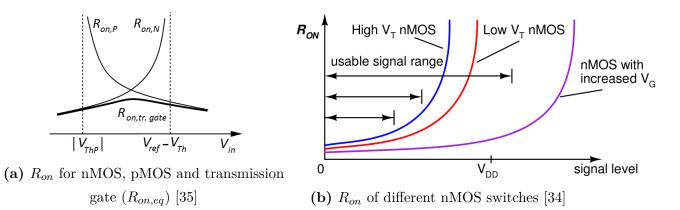

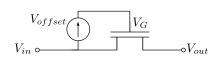

In an alternative version of this algorithm the sampled voltages are converged to higher of the two. This method would use bottom plate voltages complementary to those described above (during sampling all capacitors would be switched to  $V_{gnd}$  and based on comparator decision one of capacitors would be switched to  $V_{ref}$  each cycle). Disadvantage of such approach is the need to switch bottom plate voltages from  $V_{gnd}$  to  $V_{ref}$  during conversion – this operation is slower than switching from  $V_{ref}$  to  $V_{gnd}$  for the same size of switch due to lower mobility of holes than electrons.

Figure 3.6: Comparison of voltage on DACs top plates during conversion using classical algorithm and monotonic switching. [19]

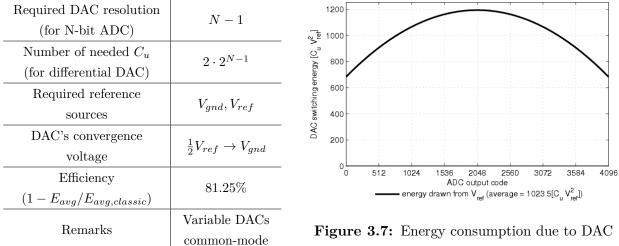

Table 3.3: Features of monotonic algorithm.

Figure 3.7: Energy consumption due to DAC switching for 12-bit ADC using monotonic algorithm.

Although monotonic switching algorithm uses half the number of unit capacitors compared to classical method (thanks to top-plate sampling required DAC's resolution can be lowered by 1 bit) and is more efficient energy-wise (by 81.25% as can be observed by comparing Figure 3.7 and 3.3) it has big disadvantage – sampled voltages common-mode gradually decreases from  $V_{cm}$  to  $V_{gnd}$ . This forces the comparator to work with very wide range of common mode degrading its performance. Overview of features of this algorithm is presented in Table 3.3.

Figure 3.8: 3-bit SAR ADC incorporating monotonic switching algorithm.

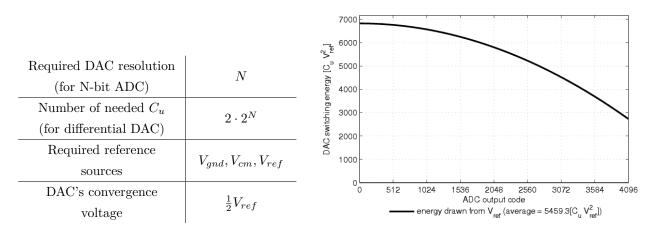

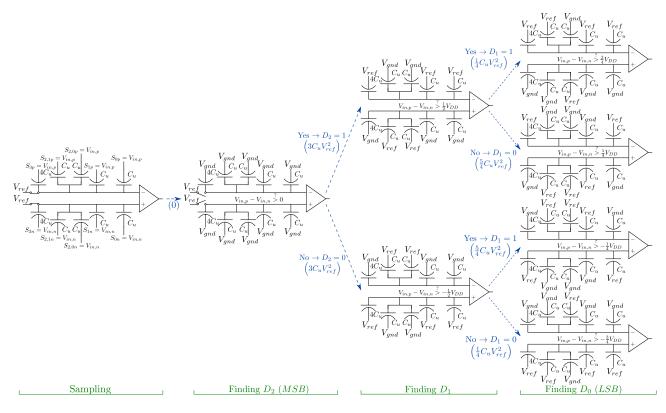

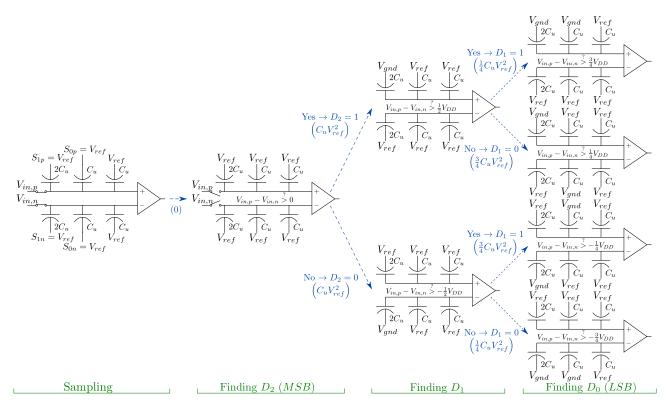

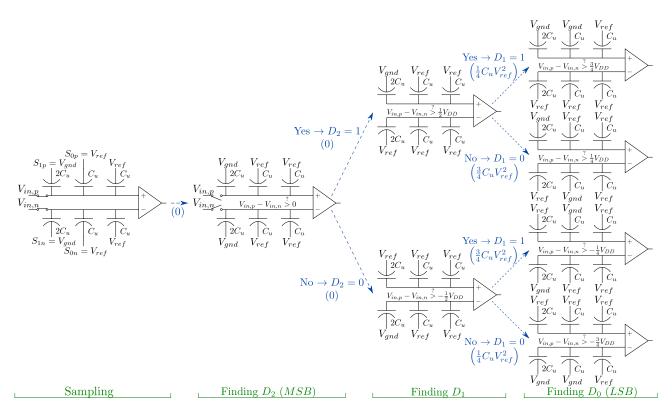

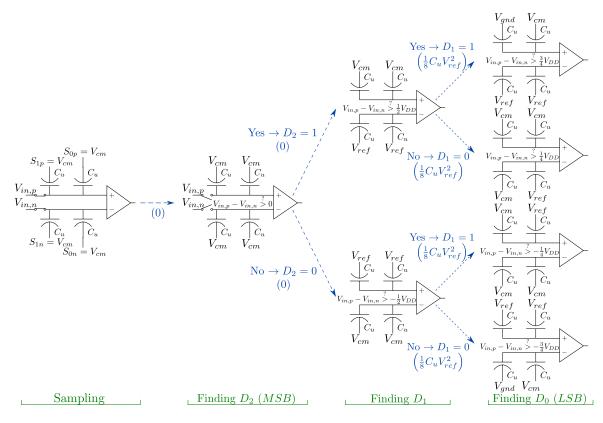

#### 3.1.4 Merged capacitor switching (MCS)

This algorithm (also called  $V_{cm}$ -based algorithm) [21, 22] uses top-plate sampling and three bottom-plate voltage levels to approximate sampled signal by converging voltage on both DACs to  $V_{cm}$ . Sampling starts with all bottom plates set to  $V_{cm}$  and sampling on top plates of capacitors. End of this phase results in switching off sampling switches and performing first comparison to find value of  $D_{N-1}$  (bottom plates remain at common mode voltage  $V_{cm}$ ):

-  $D_{N-1} = 1$  if  $V_{in,p} > V_{in,n}$ , leading to  $S_{N-2,p} \rightarrow V_{gnd}$  and  $S_{N-2,n} \rightarrow V_{ref}$

-  $D_{N-1} = 0$  if  $V_{in,p} < V_{in,n}$ , leading to  $S_{N-2,p} \rightarrow V_{ref}$  and  $S_{N-2,n} \rightarrow V_{gnd}$

After appropriate bottom plate voltages are found next comparison is performed following the same rules (as seen in example presented in Figure 3.10).

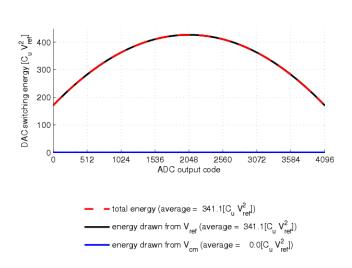

This method requires 1 bit lower DAC resolution compared to classical method (leading to lower number of capacitors needed) and is much more power efficient – comparison of Figure 3.9 and 3.3 shows 87.5% lower average energy consumption. Although additional reference voltage source  $V_{cm}$  is required, it does not need to be very accurate – it's actual voltage level does not influence differential DAC's output, it only decides DACs common-mode voltage value. Additionally no power is drawn from this source, as can be seen at Figure 3.9.

| Required DAC resolution<br>(for N-bit ADC)    | N-1                                                 |

|-----------------------------------------------|-----------------------------------------------------|

| Number of needed $C_u$                        | $2 \cdot 2^{N-1}$                                   |

| (for differential DAC)<br>Required reference  |                                                     |

| sources                                       | $V_{gnd}, V_{cm}, V_{ref}$                          |

| DAC's convergence<br>voltage                  | $V_{cm}$                                            |

| Efficiency<br>$(1 - E_{avg}/E_{avg,classic})$ | 87.5%                                               |

| Remarks                                       | $V_{cm}$ voltage<br>does not need<br>to be accurate |

Table 3.4: Features of MCS algorithm.

**Figure 3.9:** Energy consumption due to DAC switching for 12-bit ADC using MCS algorithm.

Figure 3.10: 3-bit SAR ADC incorporating merged capacitor switching (MCS) algorithm.

### 3.1.5 Early reset merged capacitor switching (EMCS)

This algorithm is an improvement of MCS algorithm focused on lowering energy consumption due to DAC switching – still top-plate sampling and three bottom-plate voltage levels are used to approximate sampled signal by converging voltage on both DACs to  $V_{cm}$ , but switching sequence is slightly modified [23].

Sampling starts with all bottom plates set to  $V_{cm}$  and sampling on top plates of capacitors.

End of this phase results in switching off sampling switches and performing first comparison to find value of  $D_{N-1}$  (bottom plates remain at common mode voltage):

- $D_{N-1} = 1$  if  $V_{in,p} > V_{in,n}$ , leading to  $S_{N-2,p} \rightarrow V_{gnd}$  and  $S_{N-2,n} \rightarrow V_{ref}$

- $D_{N-1} = 0$  if  $V_{in,p} < V_{in,n}$ , leading to  $S_{N-2,p} \rightarrow V_{ref}$  and  $S_{N-2,n} \rightarrow V_{gnd}$

Further DAC switching follows the same rules as above if  $S_{N-i,p}$  is supposed to be switched to the same voltage to which  $S_{N-i-1,p}$  is connected. Otherwise (if switching according to rules above would result in connecting those two switches to different voltages), (as seen in example presented in Figure 3.14),  $S_{N-i-1,p}$  is connected to  $V_{cm}$  and  $S_{N-i,p}$  is connected to:

- $V_{ref}$  if it was supposed to be connected to  $V_{gnd}$

- $V_{gnd}$  if it was supposed to be connected to  $V_{ref}$

Those two switching phases (switching to  $V_{cm}$  and switching to  $V_{gnd}$  or  $V_{ref}$ ) should be done one after the other (in any order), because simultaneous switching would reduce energy efficiency back to level of MCS algorithm, as presented in Figure 3.12.

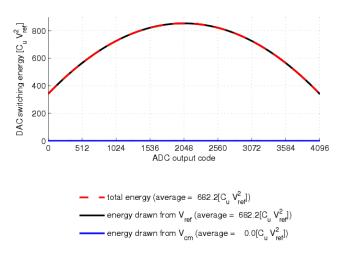

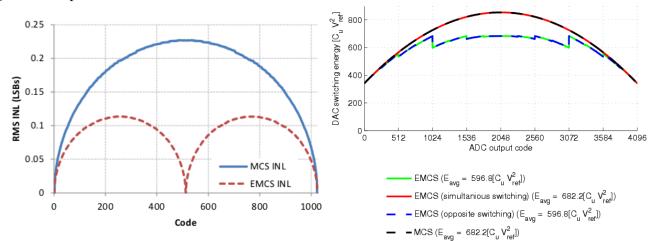

A big advantage of described method is reducing INL and DNL by removing the worst case code switching such as  $[10\cdots00] \rightarrow [01\cdots11]$ . Overall effect on INL is presented in Figure 3.11. Furthermore this method requires 1 bit lower DAC resolution compared to classical method (leading to lower number of capacitors needed) and is much more power efficient – comparison of Figure 3.13 and 3.3 shows 89.07% lower average energy consumption. Additional reference voltage source  $V_{cm}$  does not need to be very accurate – it's actual voltage level does not influence differential DAC's output, it only decides DACs common-mode voltage value. No power is drawn from this source, as can be seen at Figure 3.13. Overview of basic features of EMCS algorithm is presented in Table 3.5.

**Figure 3.11:** Comparison of INL for 10-bit ADCs using MCS and EMCS algorithm. [23]

Figure 3.12: Energy consumption for different order of DAC switching in EMCS algorithm.

| Required DAC resolution         | N-1                        |                                                                                                 |  |  |  |

|---------------------------------|----------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| (for N-bit ADC)                 | IV - I                     |                                                                                                 |  |  |  |

| Number of needed $C_u$          | $2 \cdot 2^{N-1}$          |                                                                                                 |  |  |  |

| (for differential DAC)          | 2 · 2                      | DAC Switching energy (C. v <sup>2</sup> )<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>0 |  |  |  |

| Required reference              |                            | je 300                                                                                          |  |  |  |

| sources                         | $V_{gnd}, V_{cm}, V_{ref}$ | 200                                                                                             |  |  |  |

| DAC's convergence               | IZ.                        |                                                                                                 |  |  |  |

| voltage                         | $V_{cm}$                   | 0 512 1024 1536 2048 2560 3072 3584 4096<br>ADC output code                                     |  |  |  |

| Efficiency                      | 89.07%                     |                                                                                                 |  |  |  |

| $(1 - E_{avg}/E_{avg,classic})$ | 09.0770                    | - total energy (average = $596.8[C_{II} V_{re}^2]$ )                                            |  |  |  |

|                                 | each DAC                   | energy drawn from $V_{ref}$ (average = 596.8[C <sub>u</sub> $V_{ref}^2$ ])                      |  |  |  |

| Remarks                         | switching done             | energy drawn from $V_{cm}$ (average = 0.0[C <sub>u</sub> $V_{ref}^2$ ])                         |  |  |  |

|                                 | in two steps,              |                                                                                                 |  |  |  |

|                                 | low INL                    | Figure 3.13: Energy consumption due to DAC                                                      |  |  |  |

|                                 | •                          |                                                                                                 |  |  |  |

**Table 3.5:** Features of EMCS algorithm.

switching for 12-bit ADC using EMCS algorithm.

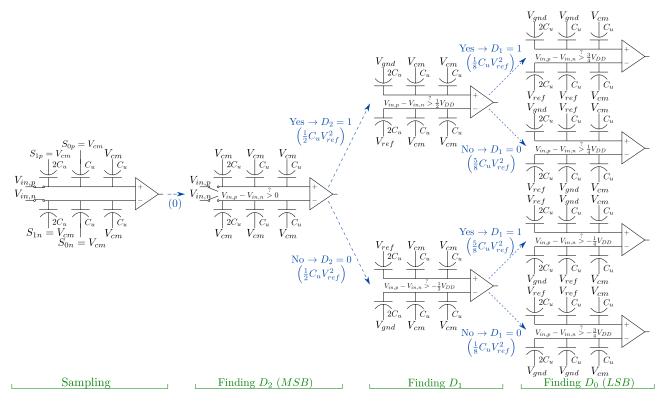

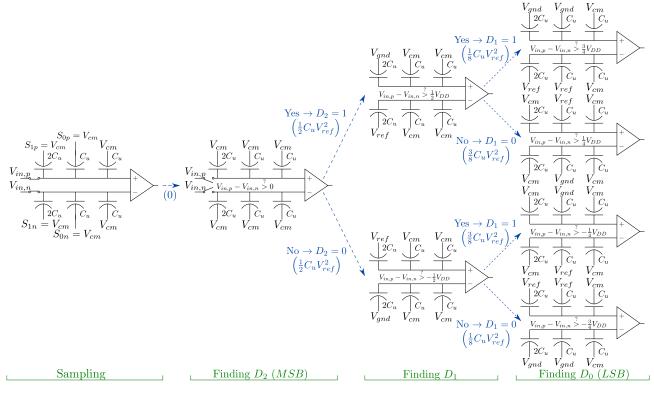

Figure 3.14: 3-bit SAR ADC incorporating early reset merged capacitor switching (EMCS) algorithm.

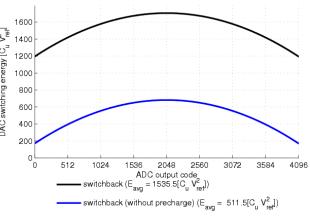

#### Asymmetric merged capacitor switching (AMCS) 3.1.6

This method (described in [24, 25]) follows exactly the same algorithm as merged capacitor switching, except for last switching of capacitors – based on value of  $D_1$  last pair of capacitor switches are set to:

- $D_1 = 1$  than  $S_{0p} \rightarrow V_{gnd}, S_{0n} \rightarrow V_{cm}$

- $D_1 = 0$  than  $S_{0p} \rightarrow V_{cm}, S_{0n} \rightarrow V_{gnd}$

One-sided switching causes the sampled voltage to converge to  $V_{cm} - LSB$  rather than to  $V_{cm}$ , but for medium and high resolution ADCs this difference is very small and should not cause a problem for comparator (unlike large variations in common mode voltage observed in monotonic switching procedure). As presented in Figure 3.16 this method requires some modification to DAC:

- unit capacitor with bottom plate at fixed potential (used in other switching algorithm to ensure fully binary voltage scaling) is removed

- capacitances connected to  $S_1$  and  $S_0$  are the same size (in both DACs), rest of capacitances are scaled in usual way in respect to  $S_1$  – this can be used either to lower the total number of used unit capacitors by half (when setting two smallest capacitance to  $C_u$ ) or to improve matching (when setting them to  $2C_u$ )

This method requires 2-bit lower DAC resolution compared to classical method (leading to much lower number of capacitors needed) and has higher efficiency – comparison of Figure 3.15 and 3.3 shows 93.75% lower average energy consumption. Additional reference voltage source  $V_{cm}$  is required and it should provide an accurate voltage level since it's actual voltage value influence differential DAC's output in the LSB bit (on the other hand in case of inaccurate  $V_{cm}$  value an error will be introduced only in last bit). Additionally no power is drawn from this third source, as can be seen at Figure 3.15. Table 3.16 summarizes the features of AMCS algorithm.

| Required DAC resolution<br>(for N-bit ADC) | N-2                                                                                                                                                                                                   |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of needed $C_u$                     | $2.2^{N-2}$                                                                                                                                                                                           |  |

| (for differential DAC)                     | $N-2$ $2 \cdot 2^{N-2}$ $V_{gnd}, V_{cm}, V_{ref}$ $V_{cm} - LSB$ 93.75% Causes common-mode changes when used with split DAC (descr. in sect. 3.33)                                                   |  |

| Required reference                         |                                                                                                                                                                                                       |  |

| sources                                    | $V_{gnd}, V_{cm}, V_{ref}$                                                                                                                                                                            |  |

| DAC's convergence                          |                                                                                                                                                                                                       |  |

| voltage                                    | $N - 2$ $\frac{N - 2}{2 \cdot 2^{N-2}}$ $\frac{V_{gnd}, V_{cm}, V_{ref}}{V_{cm} - LSB}$ $\frac{93.75\%}{Causes}$ $\frac{Causes}{common-mode}$ $\frac{changes when}{used with split}$ $DAC (descr. in$ |  |

| Efficiency                                 | 03 75%                                                                                                                                                                                                |  |

| $(1 - E_{avg}/E_{avg,classic})$            |                                                                                                                                                                                                       |  |

|                                            | Causes                                                                                                                                                                                                |  |

|                                            | common-mode                                                                                                                                                                                           |  |

| Domonla                                    | changes when                                                                                                                                                                                          |  |

| Remarks                                    | used with split                                                                                                                                                                                       |  |

|                                            | DAC (descr. in                                                                                                                                                                                        |  |

|                                            | sect. $3.33$ )                                                                                                                                                                                        |  |

Figure 3.15: Energy consumption due to DAC switching for 12-bit ADC using AMCS algorithm.

Table 3.6:

Features of AMCS algorithm.

Figure 3.16: 3-bit SAR ADC incorporating asymmetric merged capacitor switching (AMCS) algorithm.

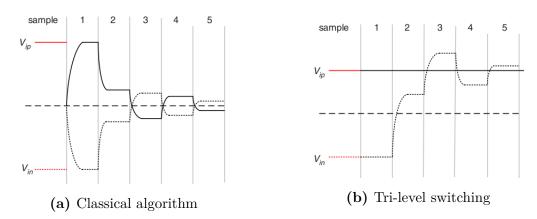

#### 3.1.7**Tri-level** switching

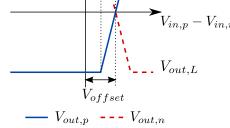

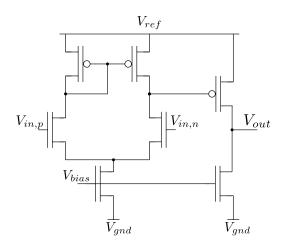

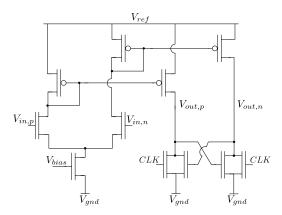

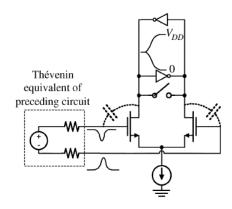

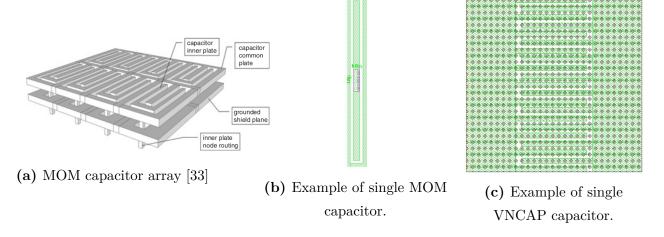

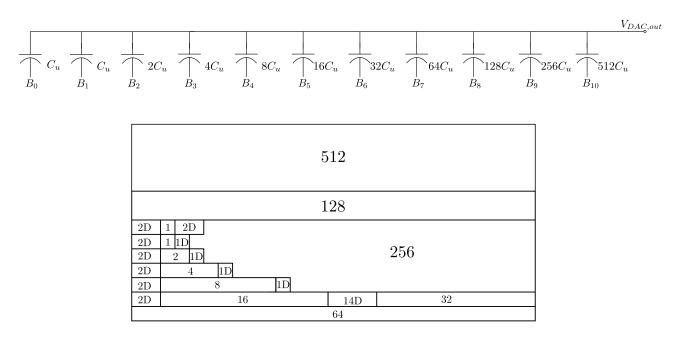

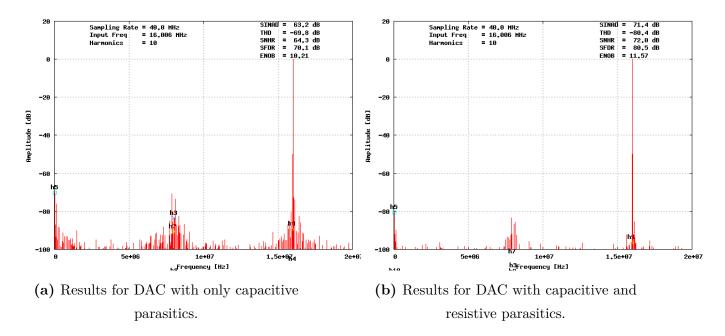

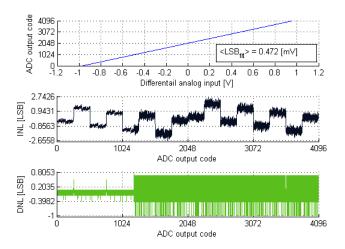

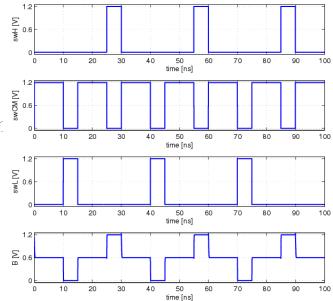

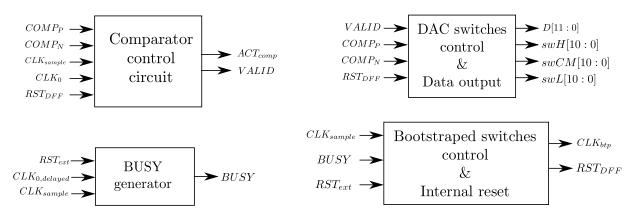

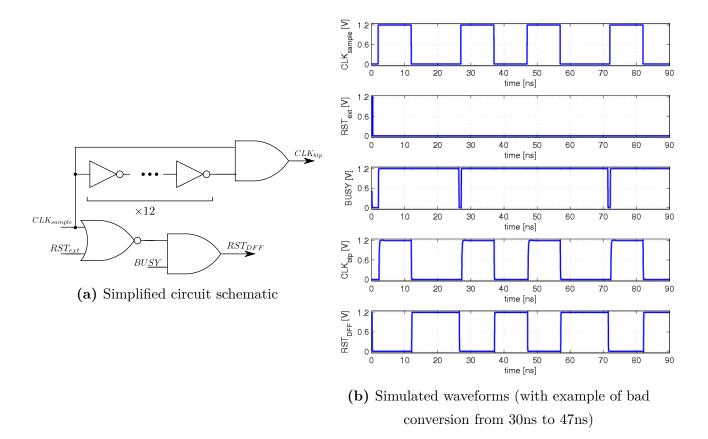

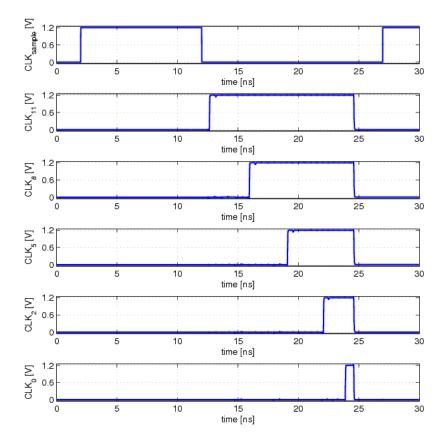

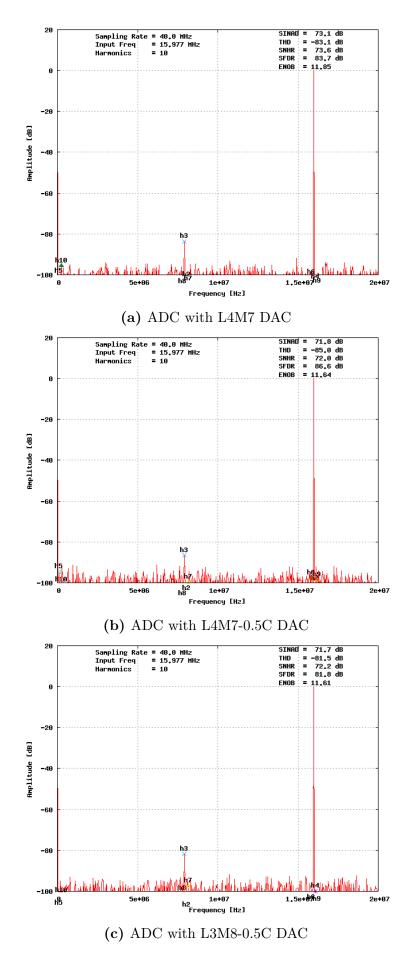

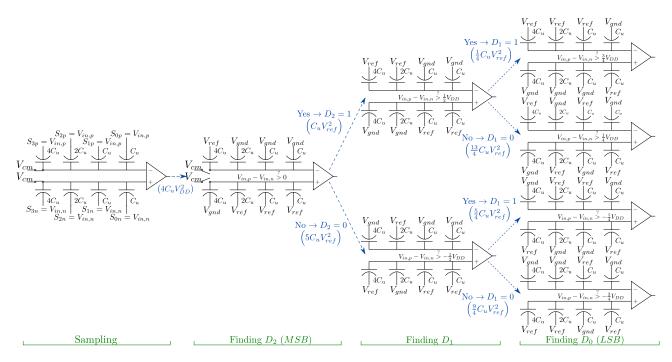

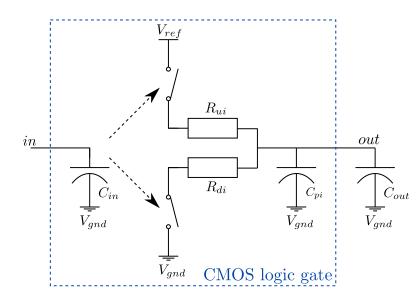

The idea behind this variation of successive approximation is based upon converging voltages sampled on DACs top plates to the voltage level of one of those samples (higher or lower one, depending on implementation) [26]. An example presenting 3-bit ADC is shown in Figure 3.19.